# 小画素系CMOSリニアイメージセンサ

Small Pixel Type CMOS Linear Image Sensor

中澤 政元\*

Masamoto NAKAZAWA

管野 透\*

Tohru KANNO

宮西 勇\*\*

Isamu MIYANISHI

白土 寛貴\*

Hiroki SHIRADO

三好 祐弥\*\*

Yuuya MIYOSHI

鈴木 淳史\*\*

Atsushi SUZUKI

## 要 旨

画素並列処理、巡回型A/Dコンバータなどの技術を適用することで、94 MHzの高速動作が可能なオールインワンタイプの小画素系CMOSリニアイメージセンサを開発した。画素サイズは4.7  $\mu\text{m} \times 4.7 \mu\text{m}$ 、外形寸法は55 mm  $\times$  10.7 mmである。また、複数のデバイス技術によりリニアイメージセンサ固有の画質課題を解消し、高画質化を実現した。

## ABSTRACT

We have developed a small pixel type CMOS linear image sensor, that can be used in an all-in-one silicon device for the high-speed operation of 94 MHz by means of pixel parallel processing architecture and cyclic analog-digital-converter technology. The pixel size is 4.7  $\mu\text{m} \times 4.7 \mu\text{m}$  and the external dimensions are 55 mm  $\times$  10.7 mm. In addition, we solved a problem peculiar to linear image sensors by using device technologies and were thus able to achieve a high image quality.

\* オフィスプリンティング開発本部 イメージング&デバイス開発センター

Imaging & Devices Development Center, Office Printing Development Division

\*\* 研究開発本部 リコー未来技術研究所 先端デバイス研究センター

Advanced Device Research & Development Center, Ricoh Institute of Future Technology, Research and Development Division

## 1. 背景と目的

近年、文書の電子化が急速に進んでいる。電子化のための入力デバイスとしてのスキャナには、高い読み取り生産性と画質、および機器の低価格化が望まれている。

複合プリンタにおいてスキャナに使用されるリニアイメージセンサはCCDが主流である。従来、高い読み取り生産性と画質が要求される高速印刷向けプリンタ層には約10  $\mu\text{m}$ ピッチの大画素系CCDが採用され、低価格が要求される中速・低速印刷向けプリンタ層には4.7  $\mu\text{m}$ ピッチの小画素系CCDが採用されてきた<sup>1)</sup>。CCDでは高画質を実現することは比較的容易であるが、高速化は困難である。これはCCDの動作原理である水平電荷転送に高電圧が必要となることや、製造プロセスの制約からトランジスタはNMOSしかないとため、回路の高速化が困難であることによる。そのため、従来のCCDでは奇数画素／偶数画素、前半画素／後半画素のように出力系統を多チャンネル化することで高速化してきた。しかしながら、出力の多チャンネル化は後段の回路規模を増大させ、部品コストの増加を招いていた。また、高画質にするための大画素系CCDでは大口径のレンズが必要となり、さらに部品コストの増加を招いていた。すなわち、CCDを用いた従来のスキャナでは高速・高画質と低コストを両立することが困難であった。

一方、近年のエリアイメージセンサでは、デジタルカメラやスマートフォンを中心にCCDからCMOSセンサへの置き換えが急速に進んでいる。高速性と高画質の最先端技術に着目すると、8K映像を持つスーパーハイビジョン (SHV) カメラ用のCMOSエリアイメージセンサも開発されている<sup>2)</sup>。Table 1にCMOSセンサとCCDの比較を示す。CMOSセンサはフォトダイオードで光電変換する点はCCDと同じだが、画素内で電荷電圧変換を行い電圧信号として読み出す点が異なる。このため、CCDで必要であった水平電荷転送は不要となり、低電圧・高速駆動が可能となる。また、CMOSプロセスを用いて製

造できることから、高速なデジタル回路や周辺回路の取り込みが可能であり、スキャナ等のイメージングシステム全体の高速化や小型化、低コスト化に利点がある。

Table 1 Comparison of specifications of CCD and CMOS image sensors.

| 項目     | CCD    | CMOS   |

|--------|--------|--------|

| 読み出し方式 | 電荷読み出し | 電圧読み出し |

| 製造プロセス | NMOS   | CMOS   |

| 高速化    | ×      | ○      |

| 小型化    | △      | ○      |

| コスト    | △      | ○      |

本論文では、高速・高画質と低コストの両立を目的とし、4.7  $\mu\text{m}$ 画素系CMOSリニアイメージセンサを開発したので報告する。

## 2. 特長

### 2-1 仕様

Fig. 1およびTable 2に、本開発のCMOSリニアイメージセンサ（以下、本センサ）の外観および仕様を示す。本センサは画素サイズ4.7  $\mu\text{m} \times 4.7 \mu\text{m}$ のカラーイメージセンサである。データレートは94 MHzと高速対応しており、低速／中速層～高速層を1つのセンサでカバーすることも可能である。色間のラインピッチは2ライン、露光方式はグローバルシャッタとしており、パッケージにはCLCC (Ceramic Leaded Chip Carrier) を採用している。また、後述するようにタイミングジェネレータ (TG: Timing Generator) やアナログ処理部 (AFE: Analog Front End) などのスキャナに必要な信号処理系を内蔵したオールインワンタイプのリニアイメージセンサである。出力はデジタル方式 (LVDS: Low Voltage Differential Signaling) であり、電源は3.3 V単一である。

以下では本センサの基本構成とそれを実現するためのコア技術について述べる。

Fig. 1 Outline of CMOS linear image sensor.

Table 2 Specification of CMOS linear image sensor of this development.

| 項目      | 仕様                               |

|---------|----------------------------------|

| カラー     | RGB                              |

| 有効画素数   | 7,400                            |

| データレート  | 94 MHz                           |

| 画素サイズ   | 4.7 $\mu$ m $\times$ 4.7 $\mu$ m |

| ラインピッチ  | 2 line                           |

| 露光方式    | グローバルシャッタ                        |

| 外形      | 55 mm $\times$ 10.7 mm           |

| パッケージ   | CLCC (84 pin)                    |

| TG, AFE | 内蔵                               |

| 出力方式    | デジタル (LVDS)                      |

| 電源      | 3.3 V                            |

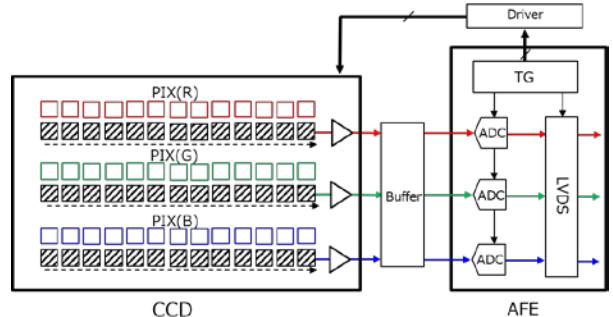

## 2-2 基本回路構成

Fig. 2にCCDを用いたスキャナ信号処理系の概略図を示す。CCDは水平電荷転送を行うシリアル処理方式であり、全体の動作速度は水平電荷転送部(斜線部)やAFE内のA/Dコンバータ(ADC)の動作速度で決まる。本センサと同じ4.7  $\mu$ m画素系CCDではデータレートで60~70 MHz程度が最大である<sup>3)</sup>。そのため、これ以上のデータレートを実現する場合は、1チャンネル当たりの動作速度は上げずに出力を多チャンネル化し、処理回路を増やす必要があった。また、CCDを用いたスキャナ信号処理系では、CCD, AFE, 駆動ドライバ, 信号バッファの部品ごとに機能が分割されたため、信号処理系全体として

の規模が必然的に大きくなり、コスト面で不利となる。

Fig. 2 Schematic diagram of scanner with CCD.

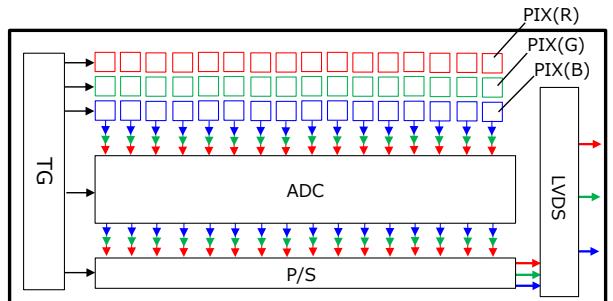

Fig. 3に本開発のCMOSリニアイメージセンサの回路構成の概略図を示す。本センサでは画像信号を並列的に処理する画素並列処理方式を採用し、これによりデータレート94 MHzを達成した。1つの処理系で対応する画素数は、規模と消費電力の観点でメリットの出るADCの速度から数画素とし、これらの画素は順次AD変換される。変換されたデジタル画像データはパラレルシリアル変換部(P/S)でシリアル化された後、LVDSで後段に伝送される。

Fig. 3 Schematic diagram of CMOS linear image sensor.

ADCを主走査方向に多数並べる画素並列処理の構成では、チップサイズを抑えるためにADCの回路規模を小さくすることが重要である。

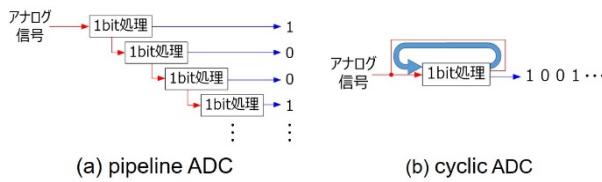

従来、AFEではパイプラインADCが用いられてきたが、本センサではADCとして中速領域で規模・消費電力のメリットが得られ易いサイクリック(巡回型)ADC<sup>2,4)</sup>を採用した。Fig. 4に巡回型ADC

の動作概念図を示す。巡回型ADCは逐次変換型ADCの一種であり、上位ビットから1ビットずつ変換し、次の変換ステージに信号を受け渡しながらデジタルデータへと変換していく点はパイプラインADCと同じである。しかしながら、パイプラインADCがビット数分の処理回路が必要となるのに対し、巡回型ADCは回路的に1ビット分で済む利点がある。これは変換結果を入力側にフィードバックすることで、Nビット分の変換動作を巡回的に行うためである。これにより回路規模を抑えることが可能となる。

Fig. 4 Schematic of ADC operation.

以上のように、本センサでは画素並列処理とそれに対応した処理画素群、および、巡回型ADCを採用することにより、Fig. 3に示すスキャナ信号処理系の高速化、および1チップ化構成を実現した。

次章では、リニアイメージセンサの高画像品質を実現するためのノイズ低減技術について詳しく述べる。

### 3. ノイズ低減技術

#### 3-1 リニアイメージセンサに対する要求画質

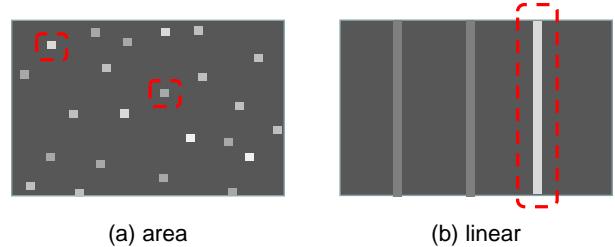

Fig. 5にエリアイメージセンサとリニアイメージセンサのノイズ画像の例を示す。ある画素にノイズが発生した場合、エリアイメージセンサではランダムな点状ノイズとして見える。しかしながら、リニアイメージセンサ（スキャナ）では一次元的にスキャンして画像を読むため、同じノイズでも縦スジになってしまふ。人間の視認性はスジのような非ラ

ンダムなレベル変化に感度が高いため、画質劣化としては影響が大きい。したがって、リニアイメージセンサではエリアイメージセンサ以上にノイズを抑制する必要がある。

Fig. 5 Comparison of pixel noise of area and linear image sensors.

#### 3-2 CDS

CMOSセンサは構造的に回路起因の固定パターンノイズ (FPN: Fixed Pattern Noise)<sup>5)</sup> が発生する。固定パターンノイズは回路のオフセット成分などに起因し、いつも決まった画素位置に発生するためリニアイメージセンサでは縦スジ要因となる。

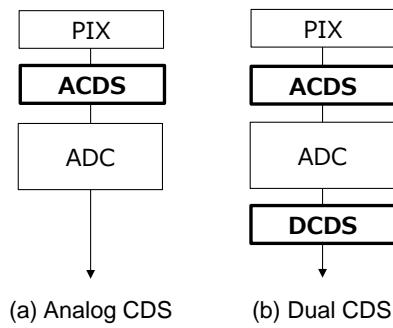

そこで、本センサでは相関二重サンプリング (CDS: Correlated Double Sampling) として、アナログ領域とデジタル領域の双方でCDSを行う二重CDS方式<sup>6)</sup> を採用した (Fig. 6)。これにより、従来のアナログCDSで補正していた画素などの固定パターンノイズに加え、ADCやアナログCDS回路自身の固定パターンノイズも補正することが可能となる。

Fig. 6 Schematic diagram of CDS.

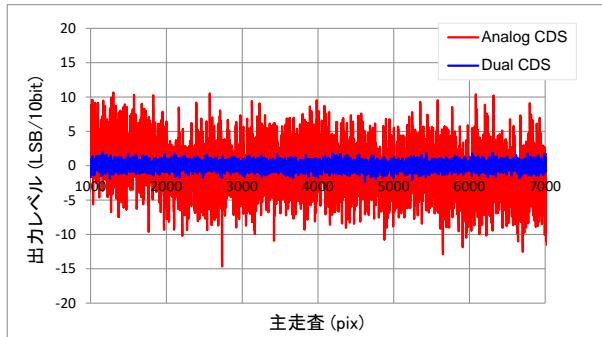

Fig. 7には固定パターンノイズの測定結果を示す。アナログCDS方式に対し、二重CDS方式では固定パターンノイズが約1/5に低減され、目標の4 LSB以下を達成した。

Fig. 7 Comparison of FPN level between analog CDS and dual CDS. (gain = 8 times, green, dark)

### 3-3 ADCダミー駆動

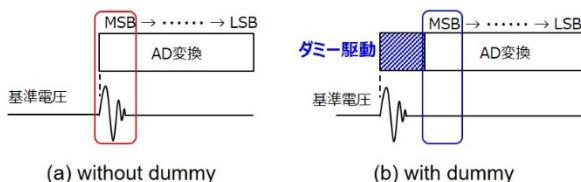

Fig. 3に示したように、本センサは多数のADCで構成され、A/D変換開始時、全てのADCが一斉に動作を開始する。このとき、最初に変換される画素においてオフセットレベルが他の画素と異なる課題が生じる。これは、画素読出動作後に最初に行われる画素の最上位ビットの変換により負荷変動が発生し、電源や基準電圧が変動するためである。

そこで、負荷変動の影響を低減するために、本センサではA/D変換前にADCを擬似動作させるダミー駆動方式を適用した。Fig. 8にダミー駆動の動作を示す。本デバイスのダミー駆動方式は最上位ビットの変換前に擬似動作を行い、負荷変動が収まった後に正規のA/D変換を実施するよう駆動した。

Fig. 8 Dummy drive of ADC.

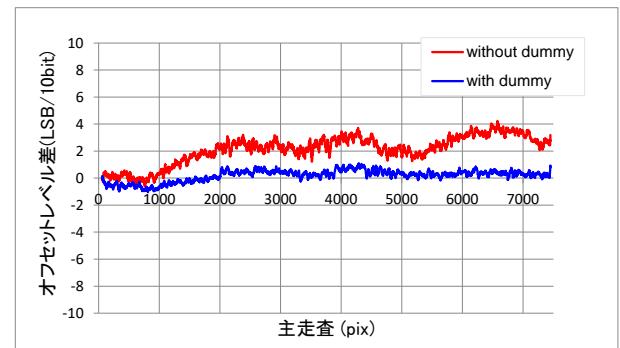

Fig. 9に最初にA/D変換される画素と次にA/D変換される画素とのオフセットレベルの差を示す。ダミー駆動方式によりオフセットレベルの差が約1/4に低減し、目標の±1 LSB以内を達成した。

Fig. 9 Comparison of even-odd difference of offset level between no-dummy and dummy drives. (gain = 8 times, red, dark)

### 3-4 欠陥起因性ノイズ対応

CMOSセンサのように微細プロセスを使用しているイメージセンサでは、回路およびトランジスタのサイズが微小となるため、シリコンウェハーの結晶欠陥に起因したノイズが顕在化する場合がある。欠陥起因性ノイズは白傷、黒傷などとも呼ばれ、製造プロセスの問題として、しばしば歩留まり低下の要因となる。

以下では、ランダム・テレグラフ・ノイズ (RTN: Random Telegraph Noise)<sup>7,8)</sup> とその低減策について述べる。

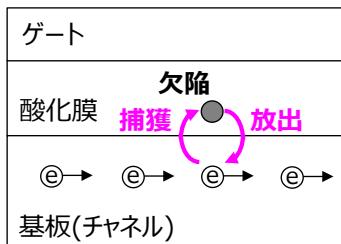

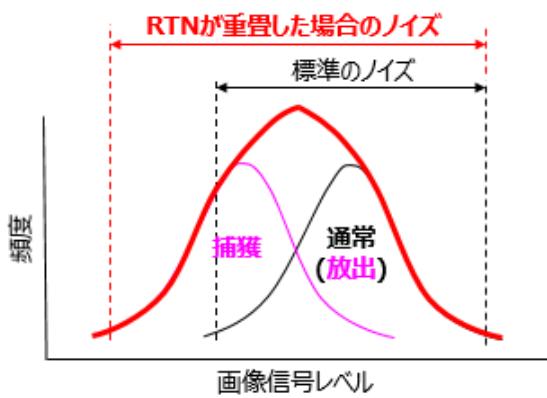

RTNは1/fノイズの一種と考えられ、MOSトランジスタのゲート酸化膜の界面準位による電子のランダムな捕獲と放出が原因とされている<sup>7,8)</sup> (Fig. 10)。このとき電子が欠陥に捕獲されている間と放出されている間とで信号レベルが異なるため、RTNを含む画素は他の画素と比べて特異的にノイズが大きく見える (Fig. 11)。

Fig. 10 RTN model.

Fig. 11 Pixel noise including RTN.

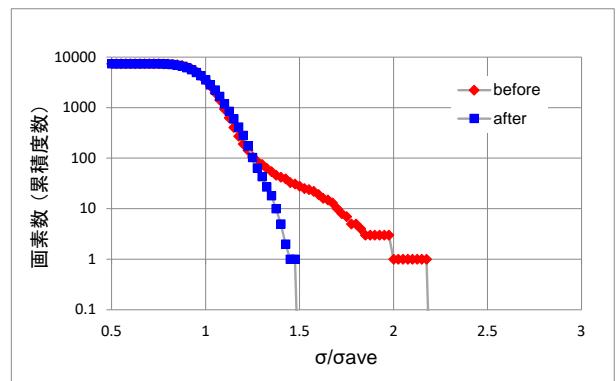

RTNへの有効策としては、欠陥の影響を相対的に低減する目的でトランジスタサイズを大きくする<sup>7)</sup>ことが知られており、我々もトランジスタサイズを従来よりも大きくすることでRTNの低減に成功した。Fig. 12に画素ノイズの結果を示す。Fig. 12はRTNを平均ノイズに対するノイズ比 ( $\sigma/\sigma_{ave}$ ) で定義し、全画素における累積度数で示している。トランジスタのサイズ変更前はノイズ比が1.3以上の画素が特異的に多い分布となっていたが、サイズ変更後にはノイズ比が正規分布に従い、特異的な画素がなくなっていることが分かる。また、Fig. 13には最適化前後の画像を示す。サイズ変更前には縦スジ状に見えていたノイズがサイズ変更後には抑制されていることが分かる。

Fig. 12 Comparison of cumulative noise distribution before and after size modification.

Fig. 13 Comparison of reading image before and after size modification. (dark, with highlight)

## 4. まとめ

本開発では、巡回型ADCを用いた画素並列処理により、94 MHz動作が可能な4.7  $\mu\text{m}$ 画素系CMOSリニアイメージセンサを開発した。特に、リニアイメージセンサにおける高画質化の課題を複数のノイズ低減技術の組み合わせにより解決し、オールインワンタイプのCMOSリニアイメージセンサを実現した。

### 参考文献

- 1) 神代敏昭ほか: 4.7  $\mu\text{m}$ カラーカメラ用CCDを用いた読み取りユニットの開発, *Ricoh Technical Report*, No. 32, pp. 83-88 (2006).

- 2) 渡部俊久ほか: 3,300万画素120fpsCMOSイメージセンサ用カラム並列2段サイクリック型A/D変換回路の低消費電力設計, 映像情報メディア学会誌, Vol. 67, No. 8, pp. J286-J295 (2013).

- 3) 東芝社, リニアイメージセンサ | 東芝半導体&ストレージ製品, <https://toshiba.semicon-storage.com/jp/product/sensor/linear-sensor.html> (参照2017-08-25).

- 4) M. Furuta et al.: A High-Speed, High-Sensitivity Digital CMOS Image Sensor With a Global Shutter and 12-bit Column-Parallel Cyclic A/D Converters, *IEEE J. Solid-State Circuits*, Vol. 42, No. 4, pp. 766-774 (2007).

- 5) 米本和也: CCD/CMOSイメージ・センサの基礎と応用, CQ出版社 (2003).

- 6) Y. Nitta et al.: High-Speed Digital Double Sampling with Analog CDS on Column Parallel ADC Architecture for Low-Noise Active Pixel Sensor, *ISSCC Dig. Tech. Papers*, pp. 500-501 (2006).

- 7) 高橋秀和: CMOSイメージセンサの低ノイズ化動向, 映像メディア学会誌, Vol. 62, No. 3, pp. 303-306 (2008).

- 8) S. Kawahito: Noise at the Circuit Level, in ISSCC 2007 Forum Noise in Imaging Systems (2007).