# 低電力デジタル温度センサーの開発

The Development for the Low Power Digital Temperature Sensor

長久 武\*

Takeshi NAGAHISA

窪田 進一\*

Shinichi KUBOTA

渡辺 博文\*

Hirobumi WATANABE

## 要 旨

二重積分型AD変換器を搭載した低電力半導体デジタル温度センサーを開発した。私たちは、従来半導体集積回路に外付けされていた二重積分型AD変換器の積分容量を集積化することにより小型化されたデジタル温度センサーを実現した。本稿では、最適設計により消費電力を類似製品に比べ1/5(115uW)に抑え、またCMOS容量のCV特性を利用しAD変換誤差を33%低減することにより、測定精度を±2°C以下に抑えた高精度デジタル温度センサーを実現したことを報告する。

## ABSTRACT

A low power digital temperature sensor with an integrated dual slope AD converter has been recently proposed. In the present study, a smaller digital temperature sensor has been realized by integrating a dual-slope capacitor, which has been usually attached to an integrated circuit device. A properly designed circuit can supply a power consumption of 115uW, 1/5 of the conventional products. We can provide the highly precise digital temperature sensors which sensing accuracy is less than ±2% by reducing 33% of AD conversion error using the CV characteristics of the CMOS capacitor.

\* グループ技術開発本部 Eデバイス開発室

Electronic Device Development Department, Corporate Technology Development Group

## 1. 背景と目的

電子機器内の各所の温度を把握し最適動作を実現することを目的として、各種温度センサーが電子機器内に組み込まれている。例えば、ラップトップ型パソコン内のCPUの周囲に温度センサーが配置され、その温度センサーは常にCPUの温度を計測している。ラップトップ型パソコンが温度センサーからCPUの温度がある一定以上を超えたという情報を受け取れば、CPUの動作を一部制限することによりCPUの温度を冷却し、パソコンの故障を防止している。

一般的に電子機器内に内蔵されているデバイス間の情報はデジタル形式で伝達されているため、計測された温度をデジタルデータで出力するデジタル温度センサーが一般的に用いられている。

近年はリチウム電池をバッテリーとするポータブル電化製品が多く発売されている。一度バッテリーを充電後、長時間使用できるポータブル電化製品が好まれるため、ポータブル電化製品に組み込まれる電子部品は自ら低消費電力であることが求められる。当然、ポータブル電化製品に搭載されるデジタル温度センサーに対しても低消費電力であることが要求される。

そこで我々は今回、消費電力を類似製品に比べ $1/5(115\mu\text{W})$ に抑えた半導体デジタル温度センサーを開発したので以下に報告する。

## 2. 技術

### 2-1 デジタル温度センサーの構成

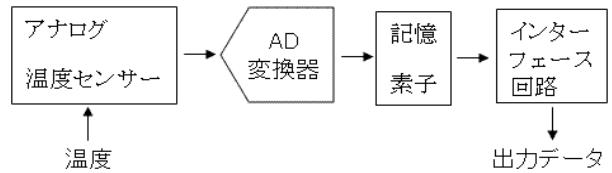

デジタル温度センサーの構成図をFig. 1に示す。デジタル温度センサーはアナログ温度センサーとAD変換器と記憶素子とインターフェース回路より構成される。

アナログ温度センサーは周囲温度に線形依存するアナログ電圧を出力する役割を担う。AD変換器は入力されたアナログ電圧を一意的に対応する数値に変換する。記憶素子はAD変換器より出力された数値データを一時

的に記憶する機能を提供する。インターフェース部は記憶素子に保持された数値データを外部に転送する役割を担う。

Fig. 1 The block diagram of the digital temperature sensor.

### 2-2 低消費電力のための試み

市場に広く流通しているデジタル温度センサーの多くは $\Sigma\Delta$ 型のAD変換器を搭載している。一般的にAD変換器で消費される電力はデジタル温度センサー全体で消費される電力の大半を占めている。ゆえにAD変換器の消費電力を抑えることは低消費電力であるデジタル温度センサーを実現することに大きく貢献する。

そこで我々はデジタル温度センサーに搭載するAD変換器に二重積分型のAD変換器を採用した。二重積分型AD変換器は $\Sigma\Delta$ 型に対して回路構成が簡単であるため消費電力を抑えることができることと、温度センサーに搭載するAD変換器であるためAD変換を高速に行なう必要がないということが二重積分型AD変換器を選択した理由である。

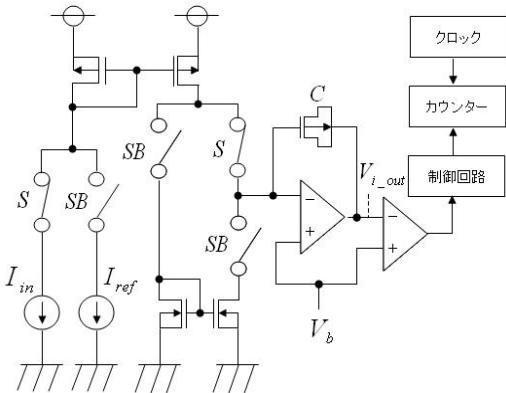

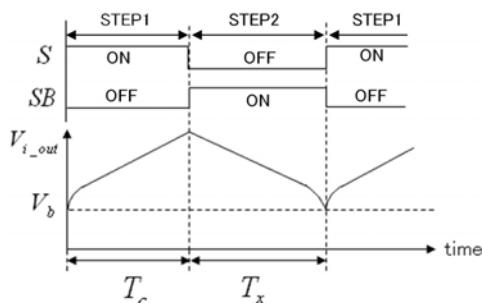

さて、以下に二重積分型AD変換器の動作概略を説明する。二重積分型AD変換器の回路構成をFig. 2に図示した。Fig. 2で図示された二重積分型AD変換器の動作は積分器の容量 $C$ (下記積分容量と表現する)に電荷を充電する過程(以下STEP1という)と積分容量 $C$ に充電された電荷を放電する過程(以下STEP2という)から構成される。STEP1ではスイッチSが導通状態となり、スイッチSBが非導通状態となる。二重積分型AD変換器に入力されたアナログ電圧 $V_{in}$ に比例する電流 $I_{in}$ ( $=V_{in}/R$ ,  $R$ は入力電圧を電流に変換する抵抗素子の抵抗値を示す。当該抵抗素子はFig. 2中に図示せず)により容量 $C$ に電荷が一定時間 $T_c$ 充電される。

Fig.2 The dual slope AD converter.

STEP2ではスイッチSBが導通状態となり、スイッチSが非導通状態となる。 $I_{in}$ に依存しない電流 $I_{ref}$ (= $V_{ref}/R$ ,  $V_{ref}$ はあるバイアス電圧)によりSTEP1にて充電された電荷をすべて放電する。積分容量 $C$ に充電された電荷をすべて放電するのに費やした時間を $T_x$ とする。いま、 $T_p$ をシステムクロックとし、 $N_x$ と $N_c$ を数値とした場合、二重積分型AD変換器に入力された電圧 $V_{in}$ は下記の式(1)から計算された式(2)に従い数値に変換される。

$$\int_0^{T_c} \frac{V_{in}}{RC} dt = \int_0^{T_x} \frac{V_{ref}}{RC} dt \quad (1)$$

$$N_x = (N_c / V_{ref}) V_{in} \quad (2)$$

ここで、 $N_x = T_x/T_p$ ,  $N_c = T_c/T_p$ である。積分器の出力電圧を $V_{i\_out}$ とするときに一連の充放電動作における $V_{i\_out}$ の電圧過渡波形をFig. 3に図示した。

Fig.3 The waveform of S, SB and  $V_{i\_out}$ .

ところで、従来は半導体基板上に二重積分型AD変換器を構成する場合、積分器の積分容量は半導体デバイスの外に取り付けられていた。近年、部品点数とコスト削減を達成するため、二重積分型AD変換器を最適設計することにより積分容量を半導体集積回路上に形成したものが数例報告されている<sup>1) 2)</sup>。そこで本開発テーマにおいても同様に積分容量を半導体集積回路上に形成した。

前述のとおり本デジタル温度センサーに二重積分型AD変換器を採用することによりAD変換器での消費電流を低減した。次に本AD変換器の動作電圧をできるだけ下げる考えたい。

本AD変換器に与える電源電圧はSTEP1が終了した時点における $V_{i\_out}$ の値(以下 $V_{top}$ という)以上であることが求められる。ゆえに $V_{top}$ の値を小さくすることが、本AD変換器に与えるべき電源電圧の低減につながる。いま $V_{top}$ は式(3)で表現される。

$$V_{top} = (I_{in}/C) N_c T_p \quad (3)$$

式(3)の右辺のうち、 $V_{top}$ を小さくするためには $I_{in}$ ,  $N_c$ ,  $T_p$ を小さくするか積分容量 $C$ を大きくすることが求められる。しかしながら、 $N_c$ はAD変換器のビット精度により固定され、システムクロック $T_p$ は消費電力の制限より下限が存在する。積分容量は半導体基板上に形成されたことにより面積が制限されるゆえ $C$ の値にも上限がある。よって $I_{in}$ のみが比較的自由に設定できるパラメータであるため $I_{in}$ をできるだけ小さくすることを試みた。検討の結果、容量 $C$ の値は120pFとし、システムクロックの値 $T_p$ を10usecとし、 $I_{in}$ の最大値を10nAと設定することにより、本AD変換器の電源電圧を2.3Vに抑えることができた。なお、 $I_{ref}$ の値は $I_{in}$ の値と同程度に設定される必要があるため、 $I_{ref}$ の値は $I_{in}$ の最大値10nAに設定した。

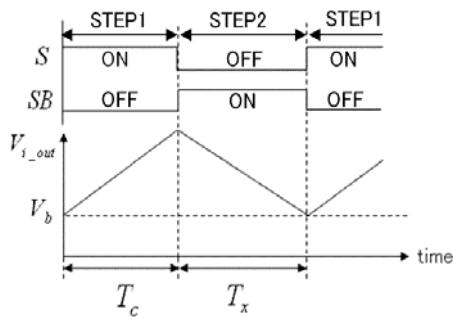

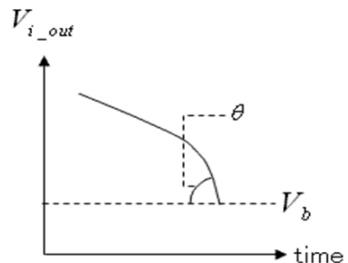

ところで二重積分型AD変換器内の積分器出力電圧 $V_{i\_out}$ にはノイズが重畠する。重畠するノイズは積分器を構成するアンプから発生する1/fノイズが支配的である。Fig. 4にSTEP2が終了する間際の $V_{i\_out}$ の波形を図示した。 $V_{i\_out}$ にて生じるノイズの実効値を $\delta$ とし、グラフ上で $V_{i\_out}$ の軌跡と $V_b$ の軌跡がなす角

度を $\theta$ とする。このとき $V_{i\_out}$ にて生じるノイズが起因で時間 $T_x$ は $\pm(U\delta)/(\tan\theta)$ の誤差を含むゆえ、 $V_{i\_out}$ に重畳するノイズにより引き起こされるAD変換誤差期待値 $E$ は下記式(4)で表現できる。ただし $U$ はある定数である。

$$E = \pm(U\delta)/(T_p \tan\theta) \quad (4)$$

本AD変換器の電源電圧を2.3Vに抑えるために $I_{in}$ ,  $I_{ref}$ を小さく設定したが、 $I_{ref}$ の値を小さくすればするほど、前述 $\theta$ の値は小さくなる。

換言すると $I_{in}$ ,  $I_{ref}$ の値を小さくすることは式(4)で示されたAD変換誤差期待値 $E$ を大きくしてしまうことにつながる。つまり、二重積分型AD変換器の動作電圧を抑えるために充放電電流 $I_{in}$ ,  $I_{ref}$ を下げたが、特に放電電流 $I_{ref}$ を下げるこによりAD変換誤差期待値 $E$ の増大という副作用が新たに生じた。

Fig.4 The  $V_{i\_out}$  waveform of the conventional dual slope AD converter.

## 2-3 AD変換誤差低減のための工夫

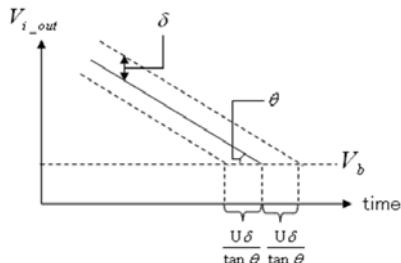

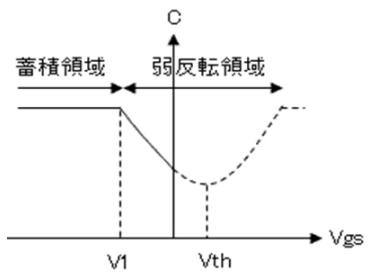

二重積分型AD変換器の最低動作電圧を2.3Vに保つつつ、前述したAD変換誤差期待値 $E$ を小さくするために、Fig. 5に示したようにSTEP2の終了直前のみ $\theta$ を向上させることを考えた。つまり、積分器出力電圧 $V_{i\_out}$ が $V_b$ に近づくほど積分容量の容量値を小さくすることによりSTEP2の終了直前のみ $\theta$ を増加させる。ここで我々はFig. 6に図示されたCMOSトランジスタ容量の2端子間の電位差により容量値が変動する性質<sup>3)</sup>（下記CV特性という）を積分容量に利用した。下記式(5)で示される弱反転領域の一部と式(6)で示される蓄積領域を動作領域として利用した。

$V_1 \leq V_{gs} \leq 0$  のとき

$$C[V_{gs}] = (WLC_{ox})/\sqrt{1+A(V_{gs}-V_1)} \quad (5)$$

$V_{gs} < V_1$  のとき

$$C[V_{gs}] = WLC_{ox} \quad (6)$$

ここで $W$ はCMOSトランジスタ容量 $C$ のチャネル幅、 $L$ はCMOSトランジスタ容量 $C$ のチャネル長、 $C_{ox}$ は単位面積あたりのゲート容量であり、 $A$ はある正の定数値であり、 $V_{gs}$ はCMOSトランジスタのゲートソース間電位差を示し、 $V_{th}$ はCMOSトランジスタが導通状態になるために最低限必要なゲートソース間電位を示し、 $V_1$ は容量値 $C$ が $V_{gs}$ に依存する領域（弱反転領域）と $V_{gs}$ に依存せず容量値が一定である領域（蓄積領域）の境界となるときの $V_{gs}$ 電圧を示す。このCV特性を利用し二重積分型AD変換器に入力された電圧を数値に変換する過程を下記に説明する。

Fig.5 The  $V_{i\_out}$  waveform of the proposed dual slope AD converter.

Fig.6 CMOS capacitance –  $V_{gs}$  dependency.

STEP1開始とともに積分容量 $C$ の $V_{gs}$ は0から小さくなる方向に動作するため、積分容量 $C$ に電荷がチャージされればされるほど積分容量 $C$ は大きくなる。ゆえに $V_{i\_out}$ の単位時間あたりの増加量は時間の経過

とともに小さくなる。やがて、積分容量  $C$  の動作領域が弱反転領域から蓄積領域に入ると積分容量  $C$  の両端の電位差による容量依存性はなくなるので  $V_{i\_out}$  の単位時間あたりの増加量は一定になる。同様にSTEP2開始時、積分容量  $C$  は蓄積領域で動作しているため  $V_{i\_out}$  の単位時間あたりの電圧減少量は一定である。やがて、積分容量  $C$  の動作領域が蓄積領域から弱反転領域に入ると放電が進むにつれ積分容量  $C$  の容量値が減少する。ゆえに  $V_{i\_out}$  が  $V_b$  に近づけば近づくほど  $V_{i\_out}$  の単位時間あたりの減少量は増えていく。

上述した  $V_{i\_out}$  の過渡特性をFig. 7に図示した。なお、CV特性を利用した積分容量を備えた本二重積分型AD変換器に入力された電圧  $V_{in}$  は式(7)の積分方程式を解くことにより得られた式(8)に従い数値に変換される。

$$\int_0^{T_c} \frac{V_{in}}{RC[V_b - V_{i\_out}]} dt = \int_0^{T_x} \frac{V_{ref}}{RC[V_b - V_{i\_out}]} dt \quad (7)$$

$$N_x = (N_c/V_{ref})V_{in} \quad (8)$$

ただし式(7)の容量  $C$  は [ ] 内の関数であることを表現している。式(8)が式(2)と一致することより CV 特性を有した容量を二重積分型変換器の積分容量として使用しても 2-2 で説明した CV 特性を有しない積分容量を用いたときと変換結果は同じであることを示している。以上の議論より 積分容量に CMOS 容量の CV 特性を利用するこにより二重積分型 AD 变換器の消費電力を増やすことなく AD 变換誤差期待値  $E$  を低減できる。

Fig.7 The waveform of S, SB, and  $V_{i\_out}$  with the use of the  $C\text{-}V_{gs}$  dependency of the CMOS capacitor.

### 3. 成果

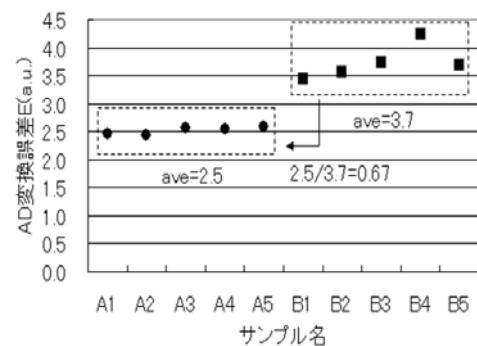

#### 3-1 CV特性利用の効果確認

前節2-3で論述した理論を実証することを目的として二重積分型AD変換器を半導体基板上に実際に試作した。2-3で説明した容量値が2端子間のバイアス電圧に依存する領域にてCMOS積分容量を使用するサンプル群をグループAとし、容量値が2端子間のバイアス電圧に依存しない領域にてCMOS積分容量を使用するサンプル群をグループBとする。グループAとグループBよりそれぞれ5つのサンプルを用意し、式(4)で示したAD変換誤差を実測した。実測の結果をFig. 8に示した。グループAより取り出したサンプルA1～A5のAD変換誤差の平均は2.5であり、グループBより取り出したサンプルB1～B5のAD変換誤差の平均は3.7であった。この測定結果より2-3で言及したCV特性を積極的に利用することによりAD変換誤差を33%低減できたことを確認した。これはデジタル温度センサーの温度測定精度を0.5°C向上させたことにつながる。

Fig.8 AD conversion errors of conventional and proposed AD converter.

### 3-2 デジタル温度センサー特性評価

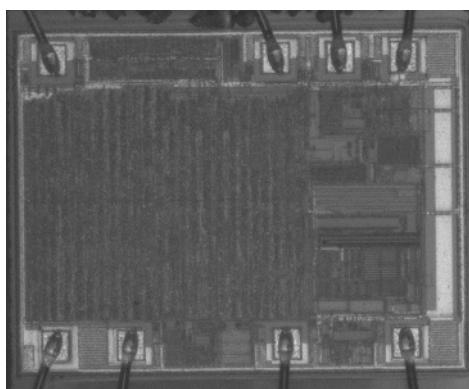

2-3で説明したCV特性を積極的に利用したAD変換器を搭載したデジタル温度センサーを0.5umCMOS半導体製造テクノロジーを用いて実際に試作し、基本特性を測定した。半導体基板上に製造した本デジタル温度センサーデバイスの写真をFig. 9に示す。またTable 1に試作品の測定結果を示す。本試作品の評価結果より、2-2で論述した二重積分型AD変換器の最適設計によってデジタル温度センサーの消費電力を115uWに抑えられたことを確認した。また、本デジタル温度センサーの変換時間（出力データを更新する時間）が30msecであることも確認した。さらに二重積分型AD変換器の積分容量にCMOSトランジスタ容量のCV特性を積極的に利用することに加え、アナログ温度センサーの出力電圧の温度特性を調節することと、AD変換器より出力された数値に適切な数値を減算することにより、周囲温度が0°Cから105°Cの範囲において±2°Cの温度精度を得ることができた。

Table 1 The characteristics of the digital temperature sensors.

| 電源電圧 | 消費電流 | 変換時間 | 温度精度   |

|------|------|------|--------|

| 2.3V | 50uA | 30ms | ±2.0°C |

Fig. 9 Chip layout.

### 4. 今後の展開

我々は半導体デジタル温度センサーに搭載するAD変換器に二重積分型AD変換器を採用し、かつ最適設計を実施することによってデジタル温度センサーの消費電力を115uWに抑えた。また、二重積分型AD変換器の積分容量をCMOSトランジスタ容量にし、かつ2端子間の電位差により容量値が変動する特性を利用することで、二重積分型AD変換器の充放電電流を微小にしたことによって引き起こされた副作用（二重積分型AD変換器の出力値がノイズの影響を受けやすくなった現象）を打ち消すことができた。

今後は、二重積分型AD変換器とアナログ温度センサーの入出力特性における非直線性誤差を小さくすることによりデジタル温度センサーの温度測定精度をさらに向上させることに取り組む。

#### 参考文献

- 1) Harish Balasubramaniam, Wjatscheslaw Galjan and Wolfgang H. Krautschneider: A Configurable Multi-Mode Dual Slope ADC in 130nm CMOS for Biomedical Signal Acquisition, In *Proc. "ProRISC 2008 Workshop"*, Veldhoven, Netherlands, (Nov. 2008).

- 2) Bruschi, P., Nizza, N., Piotto, M.: A Current-Mode, Dual Slope, Integrated Capacitance-to-Pulse Duration Converter, *Solid-State Circuits, IEEE Journal of*, pp.1884-1891, Volume 42 Issue 9, (Sep. 2007).

- 3) 岸野 正剛, 小柳 光正 : VLSI デバイスの物理 , pp. 70-72, 丸善株式会社(1986).