# MFP搭載0.13μmCu配線デバイスの故障解析

## Failure Analysis on a 0.13μm Cu Metallization Device for Multi Functional Printer

横山 弘一\* 直永 卓也\* 西垣 直彦\*\*

Koichi YOKOYAMA Takuya NAOE Naohiko NISHIGAKI

### 要 旨

LSIの故障解析において十分な実績のある解析技術であるエミッショントローリング法やOBIRCH法などのハード的な故障箇所特定手法は、電子デバイスの多層配線化に伴い困難さを増している。MFPに搭載されているLSIにおいても微細化を目的とした多層配線化が進みその故障解析は非常に難解なものとなっている。本報告ではMFP搭載の0.13μmプロセスノード8層Cu配線のプリンタコントロールLSIの故障解析において、その故障原因を特定した事例を報告する。ソフト的な故障箇所特定手法である故障診断とハード的なSEM式ナノプロービング解析技術やOBIRCH法を適用することで故障箇所の絞込みを行い、特定された故障箇所に対する物理解析結果より配線層からSi基板へのCu異常拡散起因によるゲート電極の破壊が故障原因であることを突き止めた。

### ABSTRACT

PEM (Photon Emission Microscope) and OBIRCH (Optical Beam Induced Resistance CHange) have sufficient performances as hardware failure analysis technique. However they have more challenge as the number of interconnect layers of LSIs increases. Of course, LSIs which MFP (Multi Functional Printer) employs continue to shrink and promote multilevel metallization, therefore the failure analysis on them becomes very difficult. This article reports an example of successful failure analysis of a printing control LSI fabricated by 0.13μm technology and eight-layer copper metallization. In this case, the fault was localized with Failure Diagnosis as software failure analysis technique and with SEM based nano probing technique and OBIRCH method. The subsequent physical analysis revealed the gate electrode breakdown caused by the penetration of copper in silicon substrate.

\* 電子デバイスカンパニー 品質保証部

Quality Assurance Department, Electronic Devices Company

\*\* 電子デバイスカンパニー 画像LSI開発センター

Imaging System LSI Development Center, Electronic Devices Company

## 1. 緒論

半導体デバイスの故障解析は故障箇所を絞り込むための故障箇所特定と故障原因を明らかにするための物理解析から構成されている。物理解析を実施するためには事前に故障箇所が特定されていることが必要条件となっており、エミッショングループ顕微鏡を利用した発光解析法やOBIRCH法などが十分な実績のある故障箇所特定手法として認知されている。しかしながらCu配線が採用された $0.13\text{ }\mu\text{m}$ プロセスノードを境にそれらの故障箇所特定手法は劇的に困難さを増している。上述した故障箇所特定手法は光学的要素の強い解析技術であるため、微細化に伴う分解能不足の他に多層配線化やダミー配線の存在により検出器もしくは異常箇所へ光が到達する前に遮光される確率が高くなることが大きな要因となっている。配線材による遮光を回避する方法の一つとしてSi基板面であるチップ裏面からのアプローチが考えられるが、電気的に故障を再現させた状態でチップ裏面から観察するためには原則的にパッケージがFlip Chip構造となっている必要があり、BGAやCSP、QFP、QFNなどのフェイスアップタイプパッケージへの適用は非常に困難である。

この問題の解決策として物理構造の影響を受けないソフト的な故障箇所特定手法である故障診断技術が存在感を高めている。また光学的な分解能限界に起因した故障箇所特定手法の空間分解能不足に対しては、走査電子顕微鏡(SEM)を利用した解析技術である吸収電流法が電子ビームのスポット径に依存した高い空間分解能を持つ故障箇所特定手法として期待されている。

本報告では高速動作を要求されるMFPに搭載された、8層Cu配線の $0.13\text{ }\mu\text{m}$ プロセスノードロジックLSIの故障解析を対象として取り上げ、前述の故障箇所特定手法を含めた多様な解析技術を駆使することで故障原因を導くことが出来た結果を示す。

## 2. 故障箇所特定（非破壊）

解析対象となる故障デバイスは8層Cu配線の $0.13\text{ }\mu\text{m}$ プロセスノードが採用された800万ゲート規模のMFP

搭載プリンタコントロールLSIである。故障は1サンプルのみで、LSIテスターでの再検査結果ではSCANテスト項目のみがFailしている。パッケージにはBGAが採用されており、ハード的な故障箇所特定手法では故障箇所の特定が困難であると考えられる。

### 2-1 ハード的な故障箇所特定手法

故障箇所の特定は難しいと推察されるがチップ表面から発光解析法を実施した。発光解析には浜松ホトニクス製エミッショングループ顕微鏡PHEMOS-1000を使用した。検出器としてはInGaAsおよびC-CCDが備わっている。故障状態を再現するためにテストパターンを入力した状態で実施したが良品とのエミッショングループ像比較から異常発光は確認出来なかった。同様にOBIRCH法も実施したが異常反応は確認できなかった。次に赤外域の透過光を利用したチップ裏面からの裏面発光解析法もしくは裏面OBIRCH法[1]の実施が検討されるが、この故障デバイスはBGAパッケージが採用されておりチップ裏面からのアプローチが非常に困難な構造となっている。そのため、本件においては解析対象の物理構造に依存しない故障箇所特定手法である故障診断を適用した。

### 2-2 故障診断

故障診断とはSCANテストのFail情報をもとにソフト的に故障箇所を絞り込む故障箇所特定手法である。FailしているSCAN-FFへ故障値を伝搬可能な仮定故障を追跡し、Failしている全てのSCAN-FFへ共通に伝搬可能な仮定故障が故障候補として選ばれる[2]。今回、故障診断にはMentor Graphics社のYield Assistと、指摘された故障候補にレイアウト情報を付加するLayout Aware Diagnosisオプションを利用した。診断の結果、故障候補としてscore=100のStuck-at-1故障、Cell故障、Open故障、Bridge故障が指摘された。例としてFig.1に故障診断の結果を示す。ここで、score=100とはテストログと故障シミュレーション結果に矛盾が存在せず診断結果の信用度が高いことを意味している。

```

#symptoms=1 #suspects=1 CPU_time=2338.72sec fail_log=log/SCA_N.log

#failing_patterns=49, #passing_patterns=3452

#unexplained_failing_patterns=0

symptom=1 #suspect=1 #explained_patterns=49

41 106 153 207 357 373 525 526 557 639

685 713 891 1150 1191 1273 1935 1628 1670 1713

.....

suspect score fail_match pass_mismatch type value pin_pathname cell_name net_pathname layout_status

1 /U_TOP/U_YE/P2CODE/INNER/docd02X LOCATION_IN_LAYOUT

#potential_open_segments=1, #total_segments=3, #potential_bridge_aggressors=2, #total_neighbors=35

suspect score fail_match pass_mismatch type value location layout_layer critical_area

1.1 100 49 0 CELL 1 /U_TOP/U_YE/P2CODE/INNER/U93/O KA23D

OPEN 1 B1B2_B1B3

1.2 100 49 0 OPEN 1 B1B2_B1B3

vs

1.1E-02

meta2 6.27E-02

1.3 100 49 0 DOM aggr /U_TOP/U_YE/P2CODE/INNER/LAD/s3NET690 metal2

1.4 100 49 0 DOM aggr /U_TOP/U_YE/P2CODE/INNER/DCE/s9732 metal2

.....

XMAP_TABLE_BEGIN

1.0

UNITS DISTANCE_MICRONS 2000

BRANCH1_INFORMATION_BEGIN

symptom suspect branch state pin_pathname cell_name

1 1 B1 F /U_TOP/ /U_YE/P2CODE/INNER/LAD/U18/A1 CS0F

1 1 B2 F /U_TOP/ /U_YE/P2CODE/INNER/DCE/M63/I CS0F

BRANCH1_INFORMATION_END

BRIDGE_LOCATION_BEGIN

symptom suspect layout_layer category critical_area x_cood1 y_cood1 x_cood2 y_cood2

1 1.3 metal2 S2S 1.48E-01 6002.100 8294.000 6002.300 8295.560

1 1.4 metal2 S2S 8.65E-01 6004.100 8294.840 6004.300 8295.100

...

```

Fig.1 An example of the failure diagnosis result.

### 2-3 レイアウト追跡

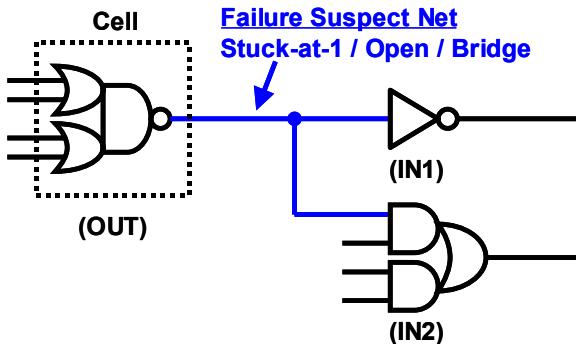

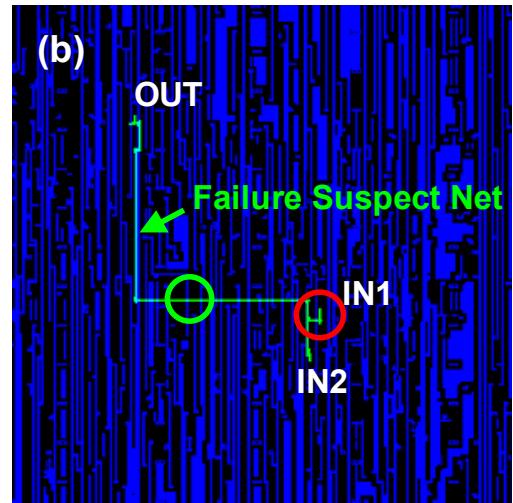

診断結果をレイアウトに落とし込むことで、全ての故障候補が1本の配線に関連していることが判明した。この配線を故障候補ネットとして着目する。Fig.2にその概略図を示す。

Fig.2 Schematic diagram of failure suspects.

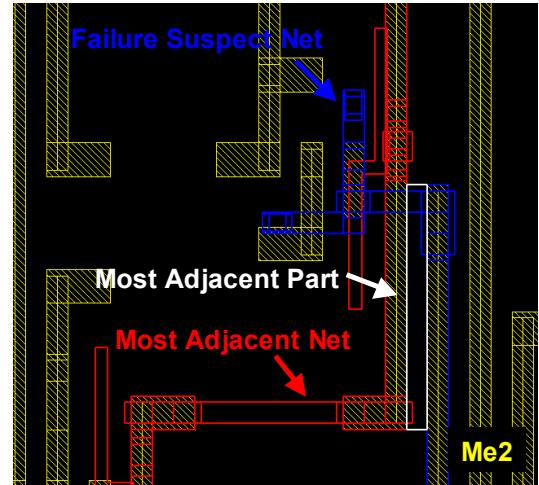

特定された故障候補ネットはLogic回路のマクロセル(OUT)の出力から他の2つのセル(IN1, IN2)の入力へと繋がる配線であり、Poly-SiからMe4までの層で構成されている。次に故障箇所候補を絞り込むため浜松ホトニクス製FA-Navigation Systemを利用し、故障候補ネットに対する最近接箇所が19箇所存在していることを確認した。最近接箇所とはデザインルール上の最小間隔でレイアウトされている配線箇所を指しており、配線間ショートが生じ易い箇所と考えられる。FA-Navigation Systemを用いて抽出された最近接箇所

の一例をFig.3に示す。一方で診断結果のLayout Aware Diagnosis機能ではBridge故障の候補箇所は12箇所指摘されている。これらの共通項をとることでBridge故障の有力候補は4箇所まで絞り込まれた。また、FA-Navigationの抽出結果よりStuck-at-1故障の有力候補となるVOC配線に対する最近接箇所が存在していないことも確認された。

Fig.3 An example of the most adjacent parts extracted by FA-Navigation system.

### 3. 故障箇所特定（半破壊）

故障候補ネットにおいて指摘のある故障モードはStuck-at-1故障、Open故障、Bridge故障と様々であり、故障箇所もBridge故障の4候補を含めた多数の箇所が候補として挙げられる。物理解析実施前に故障候補ネット上のどの箇所、どのモードで故障しているのかを明確にしておく必要があるため、半破壊的な故障箇所特定手法として吸収電流法とOBIRCH法を利用して更なる絞込みを行った。吸収電流法はOpen故障とBridge故障、OBIRCH法はStuck-at故障とBridge故障を特定することができるためこれら2手法を併用することで故障候補ネットに関して疑いのある全ての故障モードに対応することができる。吸収電流法はSEM式ナノプロービングシステムを利用して行うため1.0 μm以下のViaでも実施可能であるがOBIRCH法の実施を考慮して、不要なMe5層以上の上層配線を機械研磨処理により除去し

Via4層上にプローブ電極を形成した。電極形成で生じる電極下層のブラインドエリアの抑制、狭小なVia間スペースでの電極形成のため電極サイズは $2\mu\text{m} \times 2\mu\text{m}$ として形成した。

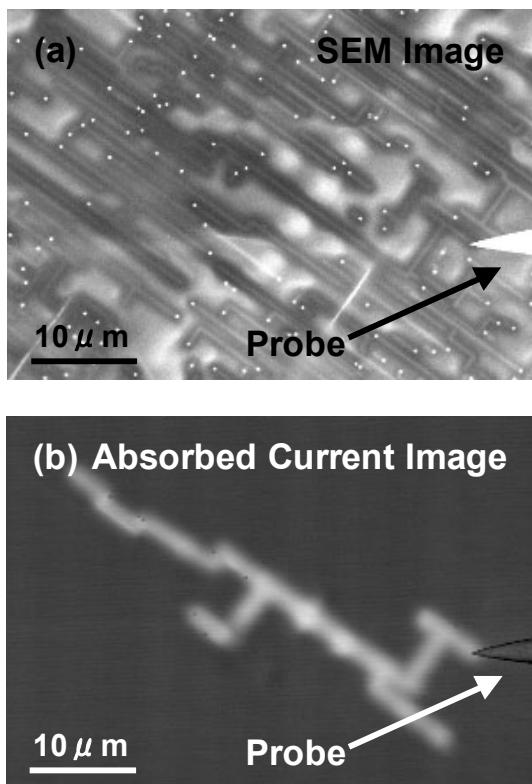

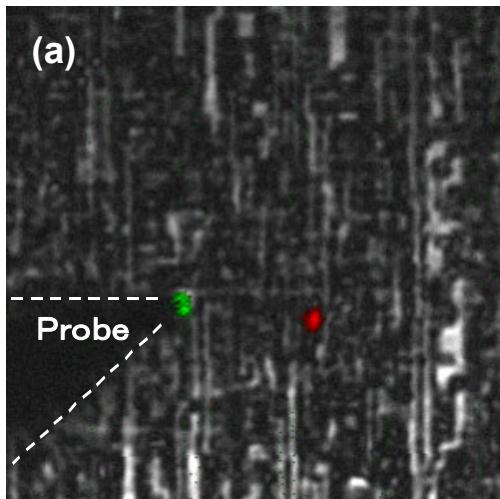

### 3-1 吸収電流法

吸収電流法はSEM装置内に搭載されたプロービングシステムをベースとしており、SEM装置内で走査された電子線の吸収電流を配線を通してプローブで検出し、電子線走査位置に対応した吸収電流値の変化を明暗コントラストで表示することでプロービングされた配線の導通状態を画像化しOpen故障やBridge故障の故障箇所を高い空間分解能で特定することができる解析技術である[3]。Fig.4に吸収電流像の一例を示す。

Fig.4 An example of the (a) SEM image and (b) absorbed current image.

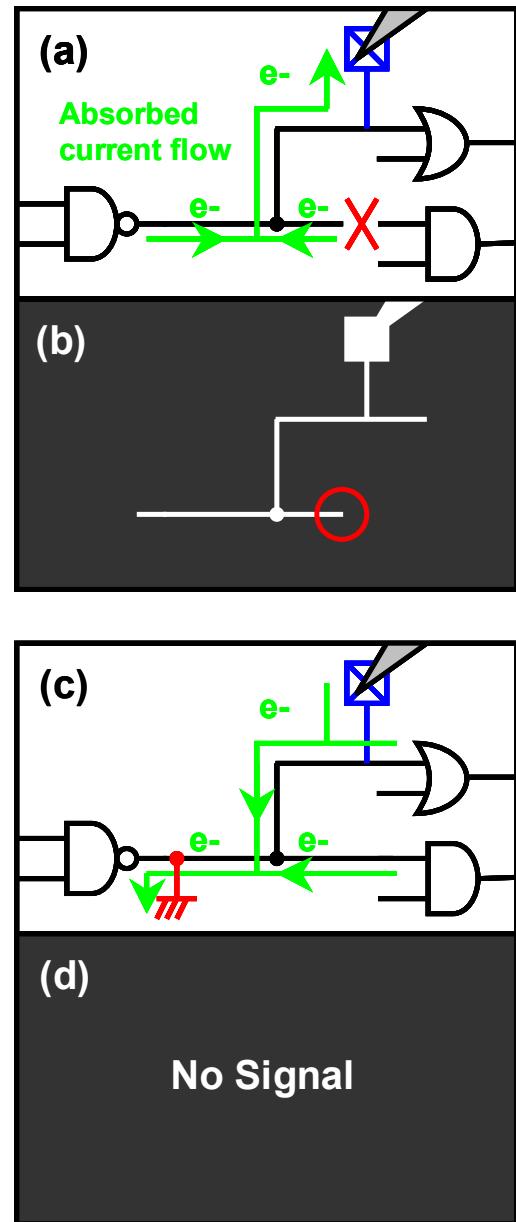

しかしプローブ電極へのプロービングではプローブや電極を含めて吸収電流像は全く検出されなかった。この結果は故障候補ネットの導通配線への吸収電流がプローブではなくVCCもしくはGNDレベルへ流れていることを示唆している。Fig.5(b), (d)に(a)Open故障と(c)Stuck-at故障のそれぞれに対応した吸収電流像の概要図を示す。

Fig.5 Schematic diagram of (a) open fault model, (c) stuck-at fault model and absorbed current image corresponding to respectively is shown in (b) and (d).

吸収電流法と故障診断結果より、この故障デバイスは故障候補ネットにおけるStuck-at-1故障である可能性が高いと判断できる。プローブ電極とVCC配線間でIV特性確認を実施しあるそ2[kΩ]の抵抗成分によるショート波形を得た。

### 3-2 OBIRCH法

吸収電流法を実施することで故障モードはStuck-at-1故障の可能性が高いと判断できたが、VCC電位とのショート箇所を絞り込むため引き続きOBIRCH法を実施した。プローブ電極には吸収電流法で使用したWPADを利用した。VCC配線を基準としてOBIRCH法を実施し、Fig.6(a)に示す箇所で異常反応を確認した。Fig.6(b)に示すレイアウトイメージとの重ね合わせから異常反応箇所がFig.2に示した故障候補ネットに繋がる2入力のうち一方のTr.箇所 (IN1) であることが判明した。事前のLayout追跡において、VCC配線に対しての最近接箇所は存在していないことが判っているためIN1のPch-Tr.での故障の可能性が高いと推測される。前述の非破壊状態でのOBIRCH法と比較するとダミー配線層を含む上層4層分の配線が除去されており、これにより異常箇所への赤外光レーザーの入射効率が向上したことが異常反応を得ることが出来た一因であると考えられる。

Fig.6 (a)OBIRCH image of failure suspect net versus VCC and (b)layout image of failure suspect net for reference.

## 4. 物理解析

故障原因を明確にするため特定された故障箇所に対して物理解析を実施した。

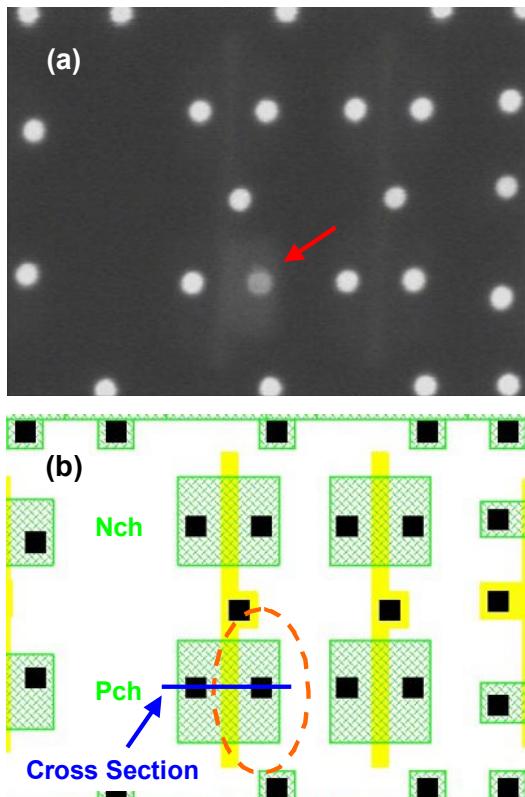

### 4-1 平面観察

故障が疑われるTr.を観察するため、平面機械研磨処理によりOBIRCH法の異常反応箇所の各層観察を実施した。最下層のMe1層が無くなるまで処理を施し、配線間ショートを疑わせる異常形状が存在しないことを確認した。一方で、Me1層除去後のSEM観察においてPch-Tr.のソース拡散エリアの異常コントラストが観察された。SEM観察像をFig.7(a)に、対応したレイアウトイメージをFig.7(b)に示す。しかしながら、この異常コントラストはPch-Tr.のゲートではなくソースであるため故障候補ネットとVCCとのショートモデルには直接的には結びつかない。ソースで観察される異常が間接的にゲートのショートを引き起こしているものと推測される。

Fig.7 (a)SEM image of contact layer at isolated fault and (b)layout image at SEM image.

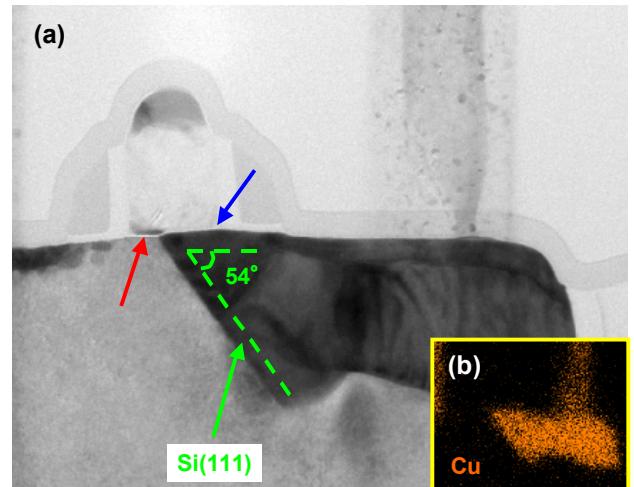

#### 4-2 断面観察

Me1層除去後の平面SEM観察においてはソース箇所の異常コントラストが観察されており、ソースの異常とゲートのショートに関連が疑われるためFig.7(b)のCross Sectionラインに示すようにソースコンタクトを含んだ面の断面TEM観察を実施し、ソース箇所で拡散異常を確認した。そのTEM像をFig.8(a)に示す。拡散異常は緑矢印で示すようにSi基板に対してSi(111)ファセット界面を形成している。また赤矢印で示す拡散異常界面とゲートPoly-Si接点箇所においてはPoly-Siへ拡散異常の影響が観察されており、青矢印で示す拡散異常とゲート酸化膜の界面形状からは拡散異常の体積膨張を読み取ることが出来る。この異常拡散に対してEDX分析を実施し、これらの拡散物質がCuであることを特定した。EDX元素マッピングではソースコンタクトからもCuが検出された一方でWは殆ど検出されなかった。Fig.8(b)にCuのEDXマッピング結果を示す。

また、ソースコンタクトの底部からは通常に存在しているSi, Ti, CoのほかにCuとTaが検出されている。

Fig.8 (a)TEM image of defect and (b)EDX mapping of Cu in TEM image.

#### 5. 故障メカニズム推定

本製品の $0.13\text{ }\mu\text{m}$ プロセスノードの配線工程にはCuデュアルダマシン構造が採用されており、Si基板に拡散しているCuは配線工程であるMe1配線由来のものであると推測される。またEDXマッピング結果よりソースコンタクトからWが殆ど検出されずCuが検出されていることやCu配線のバリアメタル成分であるTaがソースコンタクトの底部から検出されていることから、WのバリアメタルであるTiNバリア形成後のW埋め込み工程が正常に行われずMe1層形成時にコンタクトホールに対してCuが埋め込まれSi基板へと拡散したものと推測される。W埋め込み異常の原因としては異物によるマスク作用などが疑われる。また、Si基板に対するCu拡散の容易性は一般的に知られており[4-7]、Si基板中に拡散したCuは後の工程の熱処理や異常発熱を経てシリサイドを形成する。形成されたシリサイドは体積膨張を引き起こすことが報告されており[7]、シリサイドとSi(111)界面で生じたミスフィット転位によって接点箇所のゲート酸化膜が破断しゲートPoly-Si中へCuが侵入したものと推測される。これにより、故障候補ネットのゲートがVCCに対してショートしStuck-at-1故障に

至ったと考えられる。また、Cuのシリサイド化は前述のプローブ電極とVCC配線間で測定されたおよそ2[kΩ]の抵抗成分のオーミック性やその抵抗値が高いことからも説明が出来る。

- 6) G.S.Chen and S.C.Huang : J. Electrochem. Soc. 148, (2001), pp.G424-G429.

- 7) M.Seibt,et al.: phys. stat. sol.(a) 166, (1998), pp.171-182.

## 6. 結論

8層Cu配線の0.13 μ mプロセスノードが採用されたMFP搭載プリンタコントロールLSIの故障デバイスに対して故障診断、吸収電流法、OBIRCH法など様々な故障箇所特定手法を駆使することで故障箇所を絞り込むことに成功した。物理解析結果より、W埋め込み異常が引き金となりゲートがVCCとのショートに至る故障メカニズムを推定した。

本報告の事例で示した様にLSIの故障解析はプロセス技術の進歩と共に複雑化しており、多様な解析技術を駆使しなければ原因の特定に至ることは困難である。特にCu配線プロセスが適用されている製品においては故障箇所の特定が非常に困難になっており故障診断技術や吸収電流法の重要度が高まっている。

## 謝辞

Layout Aware Diagnosis評価ライセンスを提供して下さったメンター・グラフィックス・ジャパン株式会社の関係各位に感謝致します。

## 参考文献

- 1) Y.Yamada and H.Komoda : Proceedings of ISTFA, (2001), pp.305-311.

- 2) LSI テスティング学会 : LSI テスティングハンドブック, 第1版, オーム社, (2008), pp.285-294.

- 3) 水越克郎, 小山田太郎, 寄崎眞吾, 嶋瀬朗, 真島敏幸, 小柳肇, 野副真理 : LSI テスティングシンポジウム会議録, (2003), pp.213-218.

- 4) M.T.Wang, Y.C.Lin and M.C.Chen : J. Electrochem. Soc. 145, (1998), pp.2538-2544.

- 5) M.T.Wang, L.J.Chen and M.C.Chen : J. Electrochem. Soc. 146, (1999), pp.728-734.