# 低価格プリンタ/MFP向け描画アクセラレータの開発

## A Development of Drawing Accelerator for Low Cost Printer/MFP

白石 尚人\*

Naoto SHIRAIISHI

後藤 寛介\*

Hirokazu GOTOH

鈴木 正宏\*

Masahiro SUZUKI

田中 諭\*

Satoshi TANAKA

柳田 泰司\*\*

Yasushi YANAGIDA

市川 美貴也\*\*

Mikiya ICHIKAWA

### 要 旨

低価格カラープリンタ／MFPにおいては、より高速な印字を低成本で実現することが課題である。最終印字画像作成のためには多くの画像処理を行う必要があるため、高速化実現に対して従来は高速なCPUを使用する必要があり、低成本化に対するハードルとなっている。特に昨今の機器においては高画質化のため1200dpiでの描画が必要とされ、処理データ量の増大に拍車をかけており、低価格機での高速処理にはブレークスルーが必要である。

本検討では、最終印字画像の描画処理の一部をハードウェア化すること、またハードウェア化に当たってソフトウェア処理部を含む描画処理全体の並列化を考慮することで、低成本で高速な描画処理を実現した。

### ABSTRACT

When developing low-end printers/MFPs, implementing high speed printing capability at a low cost is strongly sought after. To generate a printing image, it is necessary to perform various imaging processes. For that reason, when increasing printing capability speeds, it has been difficult to lower cost, because thus far high priced CPUs with a high performance have been used. Particularly, high resolution printing images greater than 1200dpi are sought after for recent printers/MFPs, and the amount of image data being processed continues to increase.

In this study, we implemented low cost high speed image processing, by replacing a part of the processing that has thus far traditionally been done entirely by software with dedicated hardware processing, and furthermore by carrying out parallelization of the entire image processing flow.

\* コントローラ開発本部 CH開発センター

CH Development Center, Controller Development Division

\*\* MFP事業本部 GW開発センター

GW Development Center, MFP Business Group

## 1. 背景と目的

リコーのカラーレーザープリンタ/MFPでは、HP社のPCL(Printer Control Language), 自社のRPCS(Refined Printing Command Stream)などのページ記述言語(Page Description Language 以下PDL)により表現されたページデータから最終印字画像を生成している。

上記の印字画像生成処理においては、PDLの解析から最終印字画像の描画までに大量の処理を必要とする為、低価格帯のレーザープリンタ/MFPで使用されるCPUでは、処理能力不足から多くの処理時間を必要とし、印字スピード向上を難しくしている。印字スピード向上を行う為には、一般的には高速動作するCPUの採用が考えられるが、高速動作するCPUは高コストであり、また高速動作に伴い消費電力が増加してしまうという課題がある。

本検討では、ソフトウェアを含む描画処理全体の並列処理化と最終印字画像の描画処理の一部を構成する専用ハードウェア開発によって、高コストなCPUを採用せずに高速描画可能なプリンタ/MFPを実現する事を目的とした。また同時に、高速動作するCPUに比較して、消費電力の低いシステムを実現することを目的とした。

## 2. 性能向上へのアプローチ方法

従来の低価格プリンタ/MFPの多くは600dpi(dot per inch)の解像度で印字されていたが、近年ではより高解像度である1200dpiの印字を求められている。

印字データが高解像度化しても、PDLを解析する為の処理量は大きく変わらないため、PDL解析処理よりも、解析により生成された描画コマンドを読み込み描画する描画処理部分に大きな高速化が要求される。

描画処理は繰り返し処理が多い為ハード化の効果が高く、描画処理のハード化による高速化で、大きな性能向上を狙える。

また、PDL解析処理と描画処理はパイプライン化が可能である為、描画処理の高速化によって描画処理時間とPDL解析処理時間の短縮すれば、描画処理時間とPDL解析時間によって見えなくすることが可能であると考えた。

以上のことより、描画処理のハード化、およびPDL解析処理と描画処理のパイプライン化によって、プリンタ性能の向上を目指すこととした。

## 3. システム構成

### 3-1 描画アクセラレータ搭載ASIC

Fig. 1に描画アクセラレータ搭載ASICの写真を、Table 1に主な仕様を示す。

Fig. 1 A photo of ASIC with drawing accelerator.

Table 1 ASIC specification.

| 項目          | 描画アクセラレータ搭載ASIC     |

|-------------|---------------------|

| DRAMコントローラ  | DDR3 64bit 1066MHz  |

| HDDコントローラ   | SATA2               |

| DMAC        | 5ch                 |

| SDカードコントローラ | SDHC x2ch           |

| I2C         | 1ch                 |

| SPI         | 1ch                 |

| PCI Express | Gen1 x2ch           |

| 描画アクセラレータ   | ○                   |

| コピー用画像圧縮    | ○                   |

| 動作周波数       | 内部 133MHz           |

| 製造プロセス      | 65nm                |

| 電源電圧        | コア電源 1.2V IO電源 3.3V |

### 3-2 プリンタシステム全体の構成

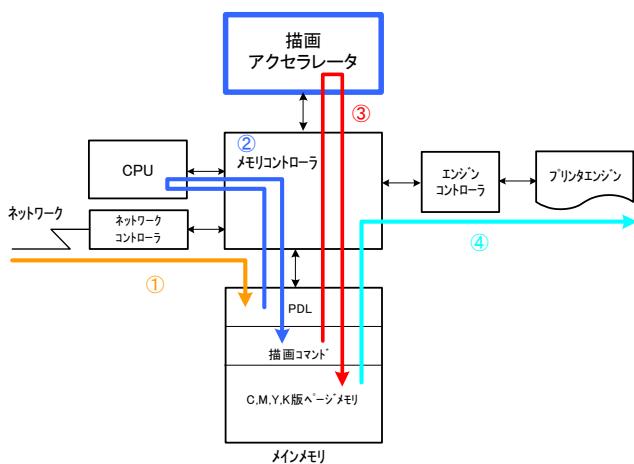

Fig. 2に今回開発したプリンタシステムの構成図を示す。MFPにおいても同じシステム構成を取る。

Fig.2 Printing system diagram.

プリンタコントローラは、ネットワークとの接続を制御するネットワークコントローラ、受け取ったPDLを解析するCPU、印字画像を描画する今回開発の描画アクセラレータ、各画像データやPDLなどを格納するメインメモリ、およびプリンタエンジンを制御するエンジンコントローラにより構成される。

以下にプリント時の処理手順を解説する。

- (1) ネットワークコントローラは、PCL, RPCSなどのPDLデータをネットワークから受け取り、メモリへ格納する。

- (2) CPUは、PDLを解析し描画コマンドを生成する。

- (3) 描画アクセラレータは、描画コマンドを読み込み、C, M, Y, K版ページメモリ領域に描画する。

- (4) エンジンコントローラはプリンタエンジンの要求に基づき、C, M, Y, K版を印字する。

### 3-3 描画アクセラレータのハード構成

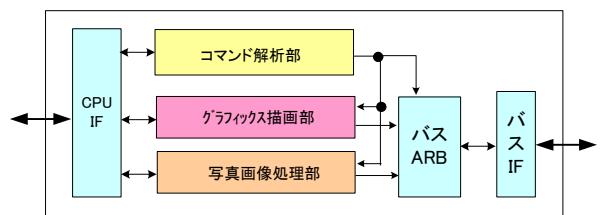

Fig. 3は描画アクセラレータのブロック図である。

Fig. 3 Block diagram of drawing accelerator.

コマンド解析部は、描画コマンドを解析し、各描画部を制御する。

グラフィックス描画部は、グラフィックス（四角形や線など）の描画を行う。

写真画像処理部は、PDL中の写真画像データを読み込み、印字用の画像処理を施した後描画を行う。

バスARB(アービタ)部は、各描画処理部を選択し、バスIF(インターフェース)を介してメモリコントローラへ接続する。

Table 2に描画アクセラレータの描画性能とゲート規模と周波数を示す。

Table 2 Drawing accelerator specification.

| 項目    | 描画アクセラレータ |

|-------|-----------|

| 描画性能  | 1Gバイト/秒   |

| ゲート規模 | 100万ゲート   |

| 動作周波数 | 133MHz    |

### 3-4 ソフトウェア構成

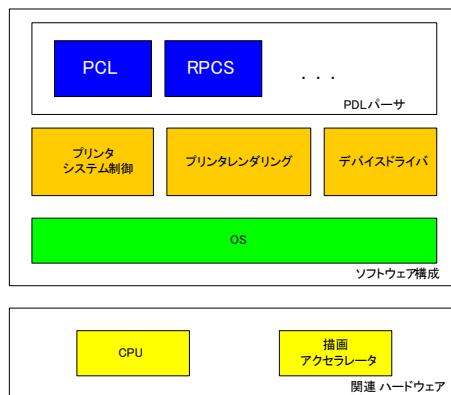

Fig. 4に本システムを構成するソフトウェア群を示す。

Fig. 4 Software schematics.

PDLデータはPCL, RPCSなどそれぞれの言語に応じたPDLパーサと呼ばれる処理モジュールによって解析処理され、プリンタレンダリング部で描画アクセラレータ向けの描画コマンドに変換される。PDL解析処理と描画処理の並列処理はプリンタレンダリング部によって制御される。

## 4. 描画処理の高速化

### 4-1 システムの並列処理

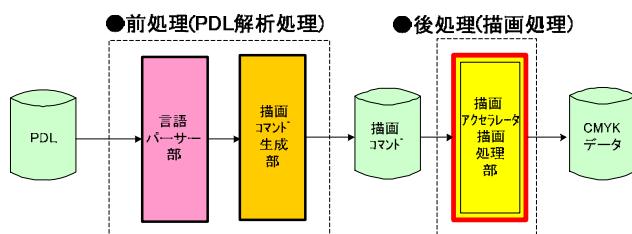

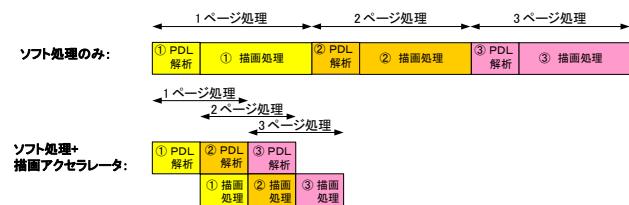

Fig. 5に描画処理フローを示す。本システムでは、プリンタ描画処理を前処理と後処理に分割し、前処理をソフトウェアで処理し、後処理を描画アクセラレータで処理する。

Fig. 5 Data flow of printer processing.

この前処理と後処理はFig. 6のようなパイプライン処理を構成し、並列動作とすることが可能である。

また、描画処理のハード化により、ソフト描画処理の2倍以上速くすることが可能となり、全体で約3倍の高速化を実現した。

Fig. 6 Timing of printer processing.

### 4-2 ハードウェアの並列処理

Fig. 3に示した描画アクセラレータの並列処理について説明する。

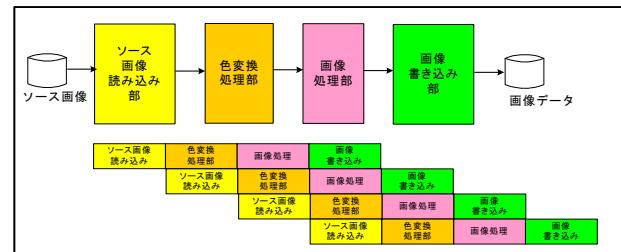

Fig. 7に描画アクセラレータにおける写真画像描画処理のパイプライン処理を示す。写真画像データを読み込み、RGB→CMYKの色変換処理と階調処理などの画像処理を順次行い、メモリへ描画する。このソース画像読み込み、色変換処理、画像処理、画像書き込みの4つの処理をパイプライン化し、並列処理を行っている。

#### ■写真画像描画パイプライン

Fig. 7 Pipeline processing of photo image drawing.

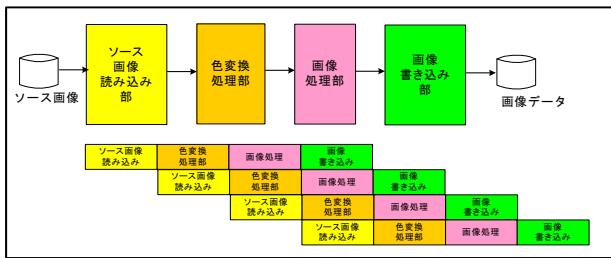

Fig. 8にグラフィックス描画処理のパイプライン処理を示す。形状情報を読み込み、形状描画処理、画像処理を順次行い、メモリへ描画する。この形状情報の読み込み、形状描画処理、画像処理、画像書き込みの4つの処理をパイプライン処理化し、並列処理を行っている。

## ■写真画像描画パイプライン

Fig. 8 Pipeline processing of graphics drawing.

以上により、ソフト描画処理に比べ2倍以上の高速処理を実現した。

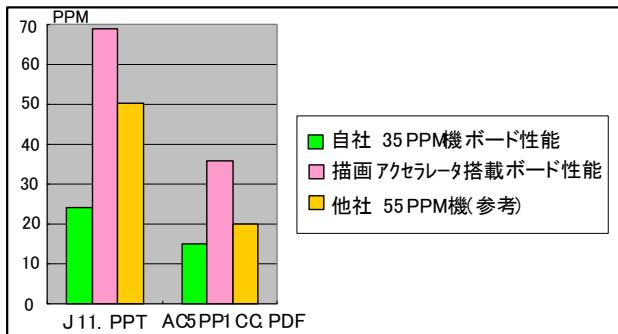

## 5. パフォーマンス比較

Fig. 9に同クラスの自他社カラーMFPのパフォーマンス比較を示す。描画アクセラレータ搭載ボードは、グラフィックス画像が多い電子情報技術産業協会(JEITA)のプリンタ用標準テスト画像J11において、自社の35PPM機ボードと同等のコストで約3倍の性能を実現できた。

写真画像が多いQualityLogic社のプリンタ評価画像であるPageSence3のAC5PP1CC画像においても、描画アクセラレータ搭載ボードは、自社の35PPM機ボードと同等のコストで約2.2倍の性能を実現できた。

これにより、上位クラス機の性能達成が可能になった。

Fig. 9 Performance comparison with other MFPs.

Fig. 10に電子情報技術産業協会(JEITA)のプリンタ用標準テストパターンのJ11とQualityLogic社のプリンタ評価画像であるPageSence3のAC5PP1CC画像を示す。

### ● J11

### ● AC5PP1CC

Fig. 10 Evaluation image.

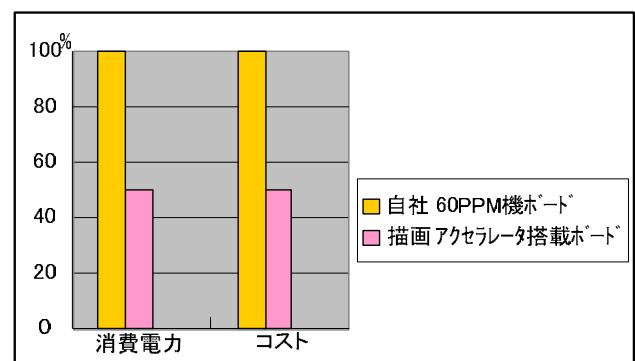

Fig. 11に消費電力とコストについて、描画アクセラレータ搭載ボードと、同等なプリンタ性能を有する自社機との比較を示す。画像処理のハードウェア化により、高速動作CPUを搭載した場合と同等の性能を、約1/2のコストと消費電力で実現可能とした。

Fig. 11 Power & cost comparison.

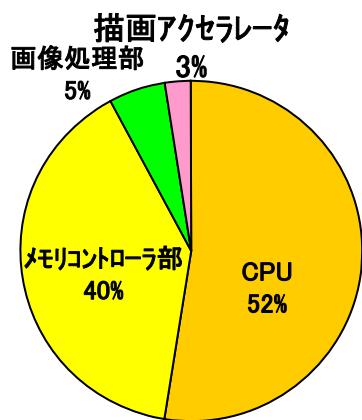

Fig. 12にコントローラにおける通常動作時の機能モジュール毎の消費電力比率を示す。

Fig. 12 Rate of electrical power consumption

コントローラ内部の消費電力はCPUが約50%を占め、メモリコントローラは高速にDDRメモリをアクセスする為約40%を占めている。一方、描画アクセラレータは全体の3%ほどの電力しか消費していない。

今回開発した描画アクセラレータは、上記の様に消費電力比率が低いにも関わらず、プリンタ性能はJ11の標準画像で約3倍の向上を実現できた。

---

## 6. 今後の展開

---

以上のように、高コストなCPUを採用せずに高速描画可能なプリンタ/MFPを実現できる、プリンタ/MFP用描画アクセラレータを開発することができた。

今後は低コストプリンタ/MFP製品への搭載を目指していく。

注1) PCLは、Hewlett-Packard companyの登録商標です。

注2) その他、文中の社名および製品名は、各社の商標、または登録商標です。