# レーザープリンタ搭載1Mbit-SRAMの故障解析手法の開発

## A Development of Failure Analysis Technique of 1Mbit SRAM for Laser Printer

遠藤 裕彦\* 直永 卓也\* 菅 也寸志\*\*

Hirohiko ENDOH Takuya NAOE Yasushi KAN

### 要 旨

LPやMFPに搭載されている半導体デバイスが故障した場合、ユーザー側で故障原因を特定することは非常に困難であり、半導体デバイスマーカーに頼らざるを得ない問題がある。しかし、半導体メモリデバイスの故障解析は、ロジック製品とは異なりメモリデバイス用のテスターなどで故障症状を再現できれば、あるbit範囲で故障箇所を特定できる。そこで、今回、新たにSRAM専用の故障解析用テスターを開発し、LPに搭載されている1Mbit-SRAMの特定rowアドレス不良に対してその故障原因を調査した。この不良は特定rowの複数アドレスにて「0」書き込み時のデータが反転する。開発した専用テスターにて故障アドレスにアクセスし、Pull-down NMOSトランジスタのVth特性がホットキャリアにより変動している事が確認され、構造解析からトランジスタのゲート長が通常の製品に比べ、小さくなっている事が分かった。

### ABSTRACT

In the case of semiconductor device failure used for LP and/or MFP, the device users have no choice but to request failure analysis (FA) to the device manufacturer because it is very difficult for device user to find defects and failure root cause. However, FA of semiconductor memory devices is different from that of logic devices. The devices user can localize failure site within certain range using a memory tester. We developed FA memory tester for SRAM, and investigated the root cause in particular row failure of 1Mbit SRAM used for LP. This failure occurs data-upset only when "0" is written in some addresses in particular row. We accessed the fault address with the memory tester we developed, and we found Vth shift of Pull-down NMOS Tr induced by hot carrier injection. Furthermore, physical analysis of Pull-down NMOS Tr made it clear that Vth shift was caused by shortening of gate length during manufacturing.

\* 電子デバイスカンパニー 品質保証部

Quality Assurance Department, Electronic Devices Company

\*\* 生産事業本部 生産統括センター

Production Strategic Center, Production Business Group

## 1. 背景と目的

様々な半導体デバイスが搭載されるLPやMFPは、個々の半導体デバイスの故障で製品の画像劣化や機能不良に陥るため、故障メカニズムを解明し、再発防止を図ることは非常に重要である。また、半導体デバイスの故障解析は微細化、多層配線化に伴い、その複雑さを増す中、SEM式ナノプローブや故障診断法といった新規の解析手法も開発され、成果を上げている<sup>1)</sup>。しかし、半導体デバイスユーザーの立場では、解析に必要な情報が入手できないこともあり、故障原因を特定することは非常に困難であり、半導体デバイスメーカーに頼らざるを得ない問題がある。また、このような要求は故障解析が難解になるにつれ増えていくことが予想される。一方、メモリデバイスはロジックデバイスの場合とは異なり、メモリテスターにて不良症状を再現し、それを解析環境と組み合わせることができれば、不良箇所をある範囲で絞り込める可能性がある。そこで、我々は専用の故障解析用テスターを開発し、LPに搭載されている1Mbit-SRAMの特定rowアドレス不良に対して故障原因の究明に成功したので報告する。

## 2. 故障デバイス概要

今回、故障解析を行ったのはLPのBCUボードに搭載される1Mbit-SRAMであり、市場稼動後約4年で機能不良に陥ったものが複数件発生した。このSRAMは複数機種に搭載されているが、不良報告を受けたのは特定機種のみであり、機種依存が見られた。これらのデバイスはボードから取り外した後、リコー及びデバイスメーカーのメモリテスターにて電気特性の不良が確認されたが、これ以上の詳細な解析結果は得られなかつた。しかし、これらの故障デバイスの市場への波及性を掴むためにも故障メカニズムの解明は重要であり、社内での解析実施となった。メモリテスターでの測定結果はMARCHパターンで最も検出率が高く、特定rowの複数アドレスにて「0」書き込み時のデータが反転するというものであった。ただし、この不良症状は不良アドレス付近への単純なファンクションパターンでも

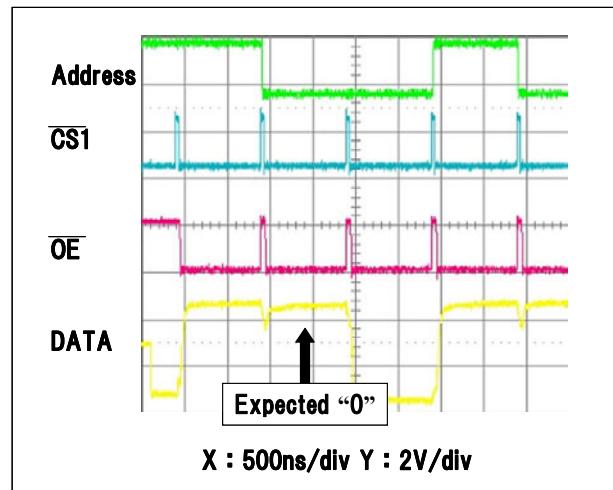

Fig.1 Read cycle waveform for a defective device.

再現することが確認されていた。Fig.1に不良アドレスの再現波形を示す。

## 3. 解析用テスター開発

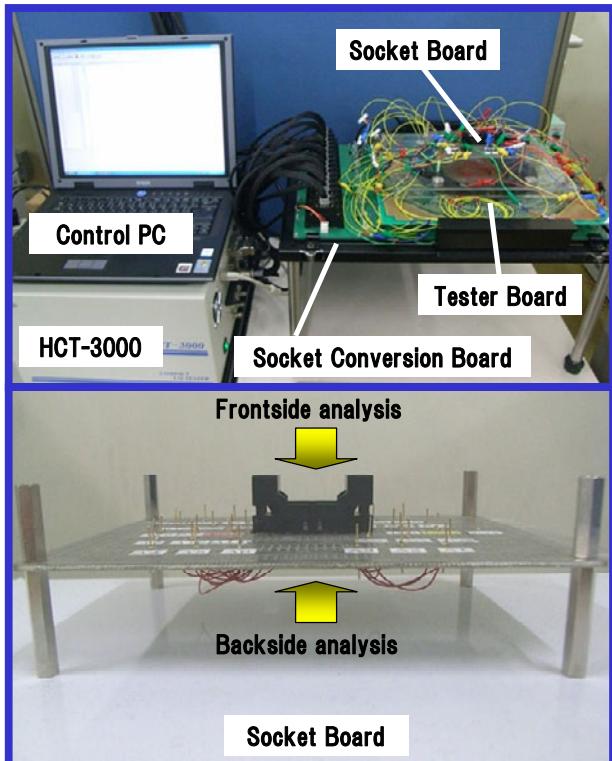

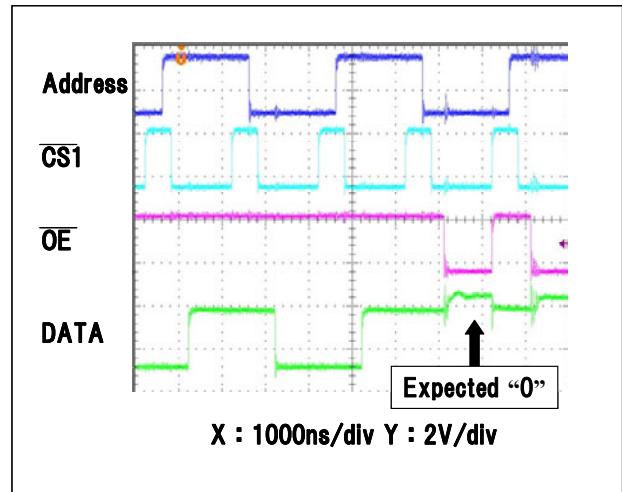

故障解析を行うためには、エミッショングループとといった箇所特定用の解析装置内で不良症状を再現させる必要がある。また故障モードによっては劣化現象を調査する必要もあり、環境試験装置内でのデバイス動作も要求される。そこで我々は既存のメモリテスターの替わりに、解析装置環境に組み込み可能なコンパクトかつデバイス仕様要求に柔軟に対応可能な解析用テスターの開発を行った。Fig.2に開発した解析用テスターの外観写真を示す。SRAMへのテストパターンの入力にはロジックデバイスの故障解析に使用している阪和電子社製信号発生器HCT-3000を使用した。この信号発生器はADVANTEST社形式等のテストパターンをHCT-3000用にコンパイルし、それぞれのテストボードを介してデバイスに印加できる装置であり、主に発光解析でのデバイス動作用に使用している。装置本体はW:330mm×D:295mm×H:200mmとコンパクトであり、信号線が最大512ピンと多ピンデバイスにも対応できる。電源は3系統で-5~10Vまで印加可能であり、印加テストパターンの最小レートは100nsで、波形タイミングやストローブタイミングは20ns単位で設定可能である。解析対象SRAMの仕様動作速度は70nsであるが、解析

に使用するには問題のないスペックであると判断した。不良症状は前述したように不良アドレス付近へのファンクションパターン印加で再現することが分かっているため、不良再現用ファンクションパターンをADVANTEST社形式のテストプログラム、テストパターンで作成した。このように自由にテストパターン編集が可能であるため、特定のエリアに絞ればメモリ用パターンの作成も可能である。通常の装置構成ではHCT-3000信号発生器からケーブルにてソケット変換ボードに接続され、テストボードを介し、ソケットボードにてデバイスにテストパターンが印加される。ここで我々はテストボードから信号線を引き出し、解析対象SRAM用のソケットボードを作成してこれと接続した。ソケットボードはデバイス表面及び裏面からの発光解析やOBIRCH解析に備え、ボード両面に配線接続できる構造にした。また、環境試験装置内で動作させる場合はソケットボードのみを投入し、配線を通じて外部から制御できるようにした。Fig.3に解析用テスターによる書き込み/読み出し波形を示す。以上のシステムを使用して不良症状の再現に成功した。

Fig.2 Photograph of FA tester.

Fig.3 Write/Read cycle waveform for a defective device with FA tester.

## 4. 実解析結果

### 4-1 故障解析手順

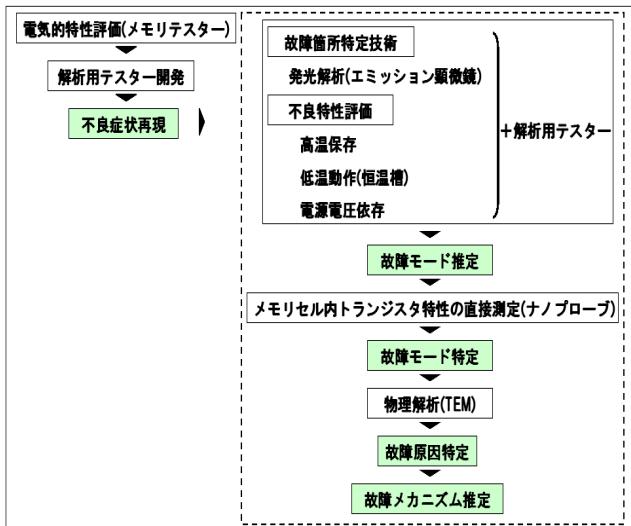

本稿で実施した故障解析手順についてFig.4に示す。まず、故障箇所特定技術として、開発した解析用テスターにてSRAMを連続動作させ、不良症状を再現させながら浜松ホトニクス社製エミッショニ顕微鏡PHEMOS-1000にてデバイス表面及び裏面から発光解析を行い、合わせて不良特性評価として高温保存、低温動作、電源電圧との関係を調査し故障モードを推測した。更にナノプローブによりメモリセル内のトランジスタ特性を直接測定することで故障モードを特定した後、物理解析による故障箇所の形状観察にて故障原因を特定し、最後に故障メカニズムの推定を行った。

Fig.4 Failure analysis flow.

#### 4-2 箇所特定技術及び不良特性評価

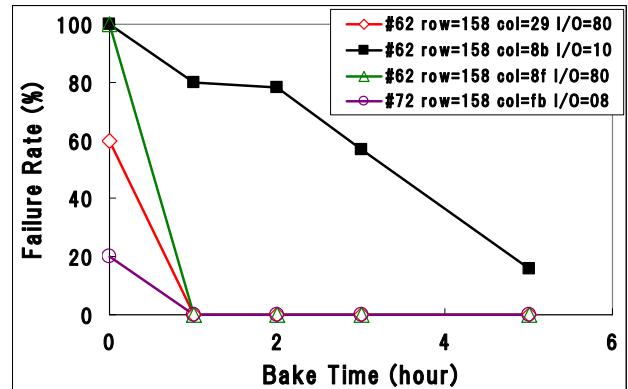

箇所特定技術である発光解析を行うにはデバイスのモールド樹脂等を除去し、デバイスチップ表面または裏面を露出させる必要があるが、デバイス裏面加工後の段階で正常状態に復帰する等不安定な現象が見られていた。デバイス加工の内容から我々はこれを熱の影響と考え、その検証のため、故障デバイスに対し高温保存評価を行った。Fig.5に示すように、150°Cのベーキングを行うと、時間経過と共に故障再現率が低下し、また、故障再現率の低下速度は同一デバイスのそれぞれのアドレスで異なることが分かった。デバイス裏面の加工には熱の影響を極力抑えるため、Ultratec社製裏面加工装置ASAP-1を使用し、デバイスは水冷により熱の影響を抑えるようにした。これによりデバイスの表面または裏面を露出した状態で不良症状が再現することが確認できたため、デバイス表面の配線パターン面及び赤外域の透過光を利用しデバイス裏面のSi基板側から発光解析を行ったが、異常発光は得られなかったため、本不良はリーク電流の増大を伴うような破壊的な故障ではないことが確認できた。一方、この故障デバイスは熱に対し不安定な症状が見られていたことから、解析用テスターのソケットボードのみを恒温槽に入れ、動作温度を-40°Cから20°Cまで変化させることで故障再現率との関係を調査した。Fig.6に示すように、

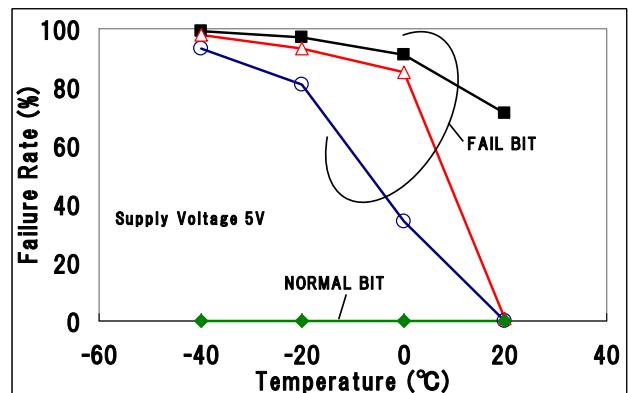

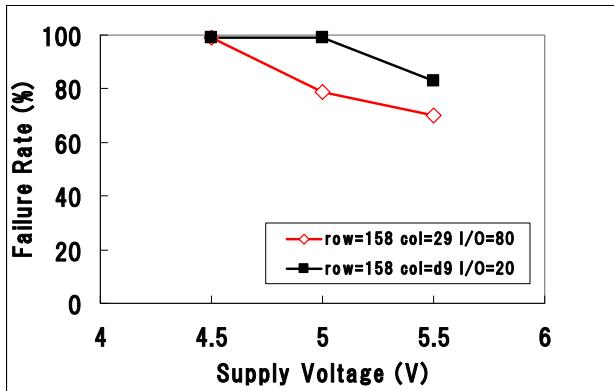

動作温度が低くなるにつれ故障再現率は高くなり、20°Cで故障が再現しないアドレスでも-40°Cでは100%近い値を示した。更に不良症状と電源電圧の関係を調査すると、Fig.7に示すように、電源電圧を低くすると故障再現率が高くなり、これらの結果から不良症状はトランジスタの動作タイミングの遅れ、即ちトランジスタ特性の変動が関係していることが考えられた。

Fig.5 Bake stress result of fail bit.

Fig.6 Failure rate dependence on operating temperature.

Fig.7 Failure rate dependence on supply voltage.

#### 4-3 トランジスタ特性評価

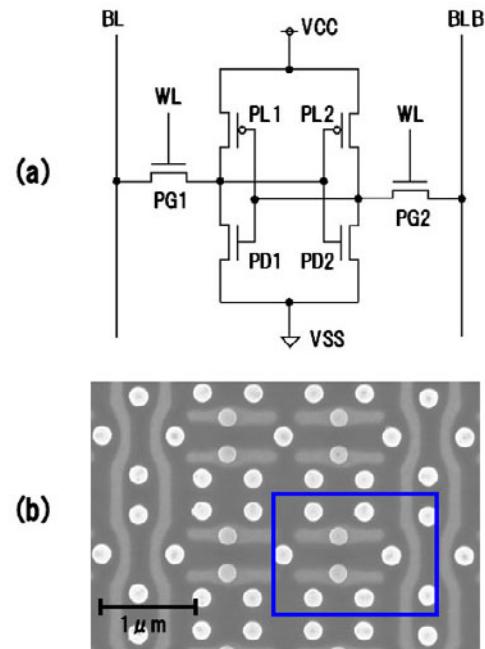

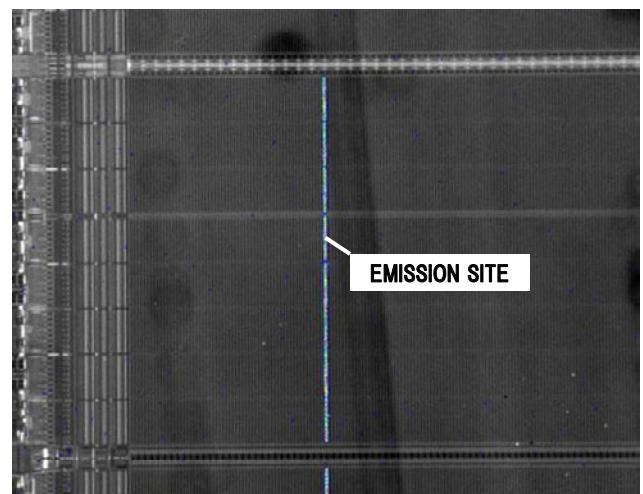

トランジスタ特性が変動している可能性が高くなり、また同一rowの個々の不良アドレスで程度差が見られることから、メモリ周辺回路ではなく、メモリセルそのものの特性が変動していることが考えられたため、メモリセルの構造解析を行ったところ、メモリセル構造はSRAMとしては一般的な6Tr-CMOS構造と判明した。メモリセルの概略図とSEM像をFig.8に示す。次に不良アドレスの物理的な位置の調査を行った。再度、開発した解析用テスターとエミッഷン顕微鏡を用い、発光解析で用いた不良症状再現用のファンクションパターンではなく、特定アドレスのみを選択し連続アクセスした時のワードラインの発光からrowアドレス位置を特定した。Fig.9の裏面からの発光解析像が示すように、特定アドレスを選択するとそのワードラインに沿ってトランジスタが発光するため、rowアドレスの物理的位置が分かる。columnアドレス位置についてはここから特定することはできなかったが、同一rowアドレスであれば不良に至っていなくとも傾向は見られると考え、任意に選択することにした。

Fig.8 6Tr-SRAM cell:(a)Schematic diagram and (b)SEM image.

Fig.9 Backside photo-emission image under active bias condition.

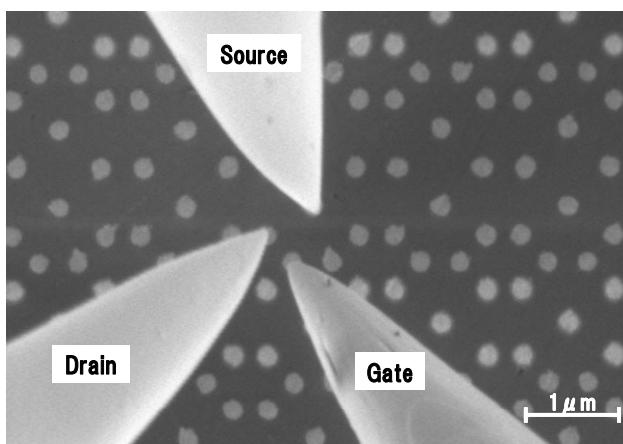

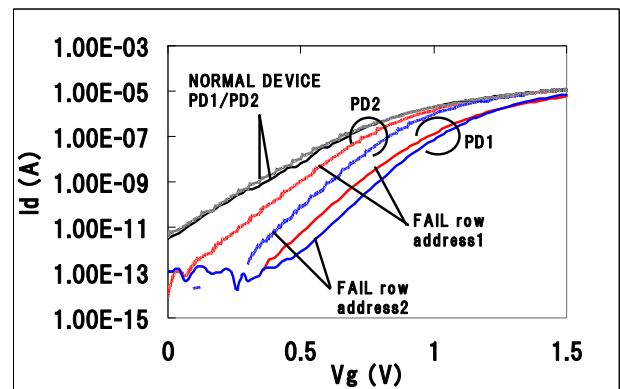

トランジスタ特性の直接測定には日立ハイテク社製SEM式ナノプローブN-6000を使用した。SEM式ナノプローブはSEMチャンバー内にメカニカルプローブを搭載し、SEM像を観察しながら微小領域へのプロービングを行うことができる装置である。Fig.10に測定時のSEM像を示す。メモリセルのトランジスタ特性を測定した結果、Fig.11が示すように、メモリセル内で対称

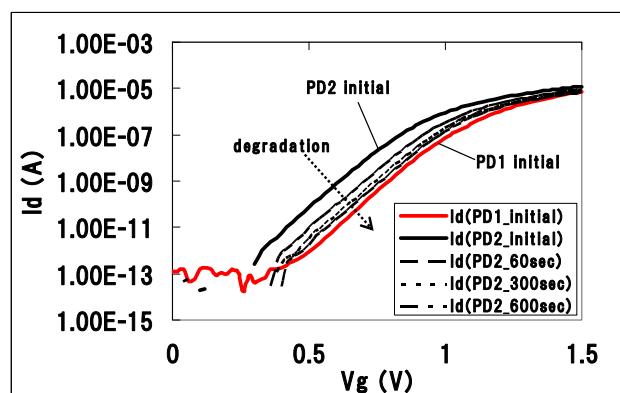

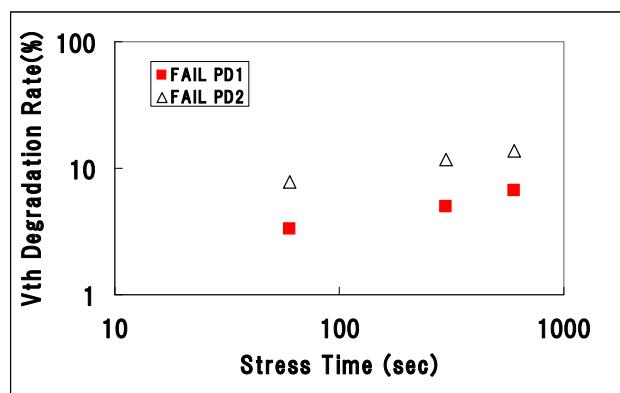

関係にあるPull-down (PD) NMOSトランジスタ1, 2のVg-Id特性から、正常デバイスは特性の差が小さいのに対し、故障デバイスは測定した2アドレス共に、PD1トランジスタのVthがPD2トランジスタに比べ約200mV高くなっていた。NMOSトランジスタのVthが高くなっていること、更にベーキングで正常復帰することから、今回の故障原因としてホットキャリアによる劣化現象が考えられたため、故障デバイスのPDトランジスタに対して、ナノプローブを使用してホットキャリアストレスを印加することで劣化傾向の調査を行った。ホットキャリアストレス条件はVd=3V、Vgは通常の動作温度領域で最も厳しい劣化を発生させるドレインアバランシェホットキャリア注入で最大劣化条件のIsubMAX時の値とした。Fig.12が示すように、PD2トランジスタにおけるVg-Id特性の変動はストレス時間と共にPD1トランジスタの初期特性に近づいていくことから、PD1トランジスタのVth変動要因はホットキャリアによるものであり、更に、Fig.13に示すPD1, PD2トランジスタのストレス時間に対するVthの変化率の傾きが同等であることから、PD1トランジスタ固有の素子性能に起因するものではないことが分かった。従って、ホットキャリアによる特定劣化は特定のトランジスタではなく、各々のトランジスタで発生する可能性があり、PDトランジスタが劣化していることで、SRAMビットセルとホットキャリアの関係から同じデータ側のPass-Gate (PG) NMOSトランジスタも劣化していることも考えられる<sup>2)</sup>。

Fig.10 SEM image of nanoprobe technique.

Fig.11 Drain current vs. Gate voltage of PD transistor measured by nanoprobe.

Fig.12 Drain current vs. Gate voltage of PD transistor and HC degradation of PD2 transistor.

Fig.13 Vth degradation rate vs. HC stress time of a pair of PD transistor for a defective device.

#### 4-4 物理解析

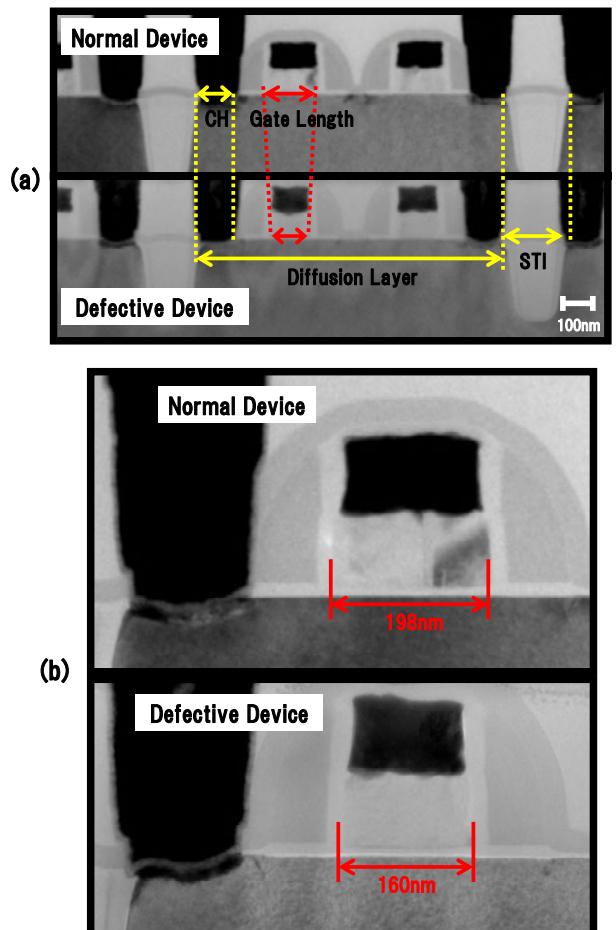

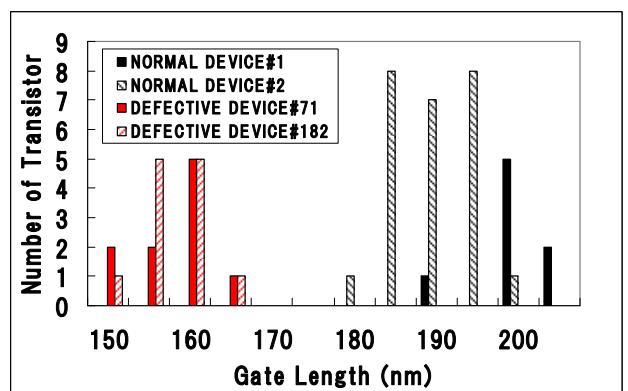

ホットキャリアによるトランジスタのV<sub>th</sub>変動が起きた原因を調査するため、トランジスタの物理解析を行った。先の解析結果において、各々のトランジスタにおいて劣化が発生する可能性があることから製造時のチップ内ばらつきではなく、ロット間ばらつきであると考えられたため、故障デバイスと、ロットの異なる正常デバイスについて断面TEM観察を行い、PDトランジスタ構造の比較を行った。Fig.14に断面TEM像を示す。LDD注入に影響を与えるゲートのサイドウォール形状や<sup>3, 4)</sup>、ゲート酸化膜等に違いは見られなかったが、ゲート長のみ、故障デバイスにおいて短くなってしまっており、正常デバイスの70~90%になっていることが分かった。複数チップのゲート長のばらつきをまとめたFig.15が示すように、正常デバイスと故障デバイスの分布には隔たりが見られることから、ゲート長の異なるメモリ周辺回路についても比較を行ったところ、ビットセルと同様に故障デバイスでゲート長が短くなっていることを確認した。従って、故障デバイスは仕様に対しゲート長が異常に短く形成されており、これがPDトランジスタのホットキャリア耐性を下げた原因であると考えられる。

#### 4-5 故障メカニズムの推定

以上の結果から故障発生のメカニズムは次のように考えられる。ロット間ばらつきとしてゲート長が異常に短く形成されたデバイスにおいて、LP側から頻繁にアクセスする特定rowアドレスでメモリセルの片側のPG、PDトランジスタにてホットキャリアが発生し、V<sub>th</sub>が高電圧側に変動することで「0」書き込みまたは読み出しができなくなった。この時、「1」書き込みでは不良として検知されない。これは市場稼動後一定期において故障として検知されることや、故障が発生するLPに機種差が見られることとも合致する。

Fig.14 Comparison of TEM cross section image of PD transistor between normal device and defective device : (a) magnification 10k and (b) magnification 30k.

Fig.15 Gate length distribution of PD transistor for normal device and defective device.

## 5. 結論

LPに搭載される1Mbit-SRAMに対し、SRAM専用の解析用テスターを開発することで故障解析を可能にし、トランジスタのVthがホットキャリアにより変動していくことが分かった。また、その原因としてトランジスタのゲート長が正常デバイスと比べ短くなっていることを突き止めた。解析用テスターをエミッショングラフ等解析装置と組み合わせることにより故障解析の箇所特定技術として使用することができ、半導体デバイスユーザー側でも不良箇所を絞り込むことができるこことを示した。これによりメーカー側へ発生原因の調査を依頼し、またユーザー側として市場への波及効果の推定に役立てた。動作スペックに関しても解析利用であれば十分使用できることを確認できたため、今後、この解析用テスターを使用し、他のメモリデバイスの故障解析への応用も期待できる。

### 謝辞

本研究を行うにあたり、ナノプローブの測定にご協力頂いた株式会社日立ハイテクノロジーズの関係各位に深く感謝致します。

### 参考文献

- 1) 横山弘一、直永卓也、西垣直彦：MFP 搭載  $0.13\mu$  m Cu 配線デバイスの故障解析、Ricoh Technical Report, No.36, (2010), pp.85-91.

- 2) Th. Fischer et al.:Impact of process variation and long term degradation on 6T-SRAM cells, Advances in Radio Science, Vol.5, (2007), pp.321-325.

- 3) P. Egger, S. Muller, M. Stifter: A New Approach for SRAM Soft Defect Root Cause Identification, ISTFA, (2007), pp.14-19.

- 4) H. Lin, C. Chen: An Application of a Nanoprobe Technique in the Characterization of Advanced SRAM Devices, ISTFA, (2008), pp.417-422.