# ハードウェアモデリング手法によるPCIeの性能予測

## Hardware Modeling Methodology for Performance Estimation of PCIe

池田 純一\*

Junichi IKEDA

### 要　　旨

組み込みシステムの複雑化に伴い、LSIなどのハードウェア設計においてもシステムレベルの効率的な設計手法が渴望されている。近年のシステムレベル設計では記述が簡単なC言語ベースのハードウェアモデルが主流となり、ソフトウェアとの協調設計や演算アルゴリズムの高位合成の分野で実用化が始まった。しかし、これらの分野のモデリング手法はハードウェア構造やタイミングを抽象化することが前提となっており、様々なハードウェアシステムの性能を比較することが難しいという課題があった。このため、我々はハードウェアシステムの性能予測を主目的として、ハードウェア構造やタイミングに関する抽象度を下げる一方、データ構成や機能の抽象度を上げることで、単純な記述で精度の高い性能予測が可能な、独自のハードウェアモデリング手法を考案した。本稿では、PCIe (PCI Express) 通信コアモデルによるデータ転送性能評価を題材に、ハードウェア性能予測向けモデリング手法の適用効果を報告する。

### ABSTRACT

In recent years, as the complexities of the embedded system increase, efficiency of system-level design becomes the one of the most important part of the hardware system development such as system LSI design. Among many system-level design methodologies, C-based hardware modeling is becoming the mainstream and several practical examples have been reported in field of Co-design of hardware and software, and high-level synthesis of arithmetic algorithms. In spite of those practical examples, above methodologies are not suitable to estimate performance of hardware architectures, since modeling methodology in above fields is based on abstraction of the hardware structures and timings.

In this paper, we propose a new hardware modeling methodology which can be used to estimate performance of hardware architectures. The proposed method is based on the high-level abstraction of the data structure and functionality, and low-level abstraction of hardware structure and timings, so that it satisfies both simple description and accurate performance estimation. Modeling of the PCI Express system is shown to illustrate the validity of the method.

\* 研究開発本部 東北研究所

Tohoku R&D Center, Research and Development Group

# 1. 背景と目的

## 1-1 はじめに

近年の組み込みシステムの大規模・複雑化と通信技術をはじめとするさまざまな技術革新に伴い、システムレベルの効率的な設計手法の重要性が高まっている。特に性能未達成によるLSIなどのハードウェア開発の手戻りが発生すると、膨大な修正期間とコストが必要となる。このため、回路設計前の早い段階で正確にシステム性能を予測することが、システムレベルの設計手法における重要課題のひとつとなっている。本稿では、デジタルカラー複合機（MFP）におけるPCI Express（PCIe）の導入に際して考案した独自の性能予測向けハードウェアモデリング手法と、設計上流工程におけるシステム性能評価の適用効果について報告する。

## 1-2 デジタルカラー複合機におけるPCIeの導入

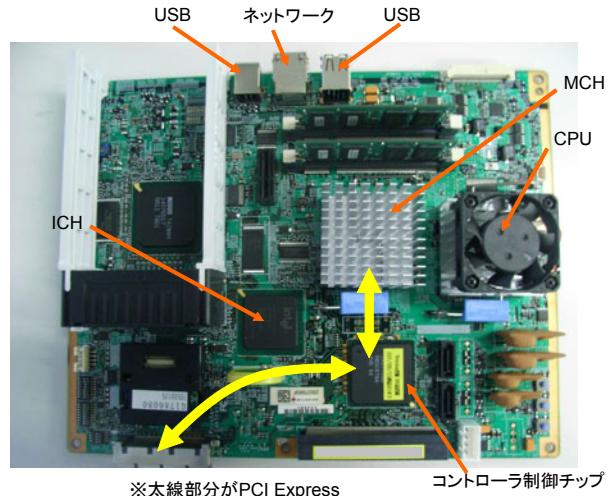

Fig.1にデジタルカラー複合機（MFP）の主力機種に搭載されている、PCI Expressを2ポート持つ制御チップを搭載したコントローラボードを示す。PCI Expressは、パラレル方式のPCIバスに代わる新たな高速シリアルインターフェースとして、PCI-SIG（Peripheral Component Interconnect-Special Interest Group）により2002年に最初の仕様が公表された通信規格である<sup>1)</sup>。従来のPCIバス（64bit）は100本以上の信号線で533MB/secの理論限界性能を有していたのに対し、PCI Express（4レーン）は16本の信号線で双方向合わせて2GB/secの理論限界性能を発揮し、信号線の簡素化・バスの高速化を両立することができる。

PCI Expressを搭載したコントローラ制御ボードは印刷速度の向上に大きく貢献しているが、ボード信号路レイアウト・LSIパッケージングはもとより論理層の回路設計にも多くの難易度の高い技術課題があった。本稿で報告するハードウェアモデリング手法は、PCI Expressの論理層設計における性能を正確に予測することを目的として考案した手法である。

Fig.1 MFP Controller Board using PCIe.

## 1-3 PCIe導入の課題

MFPに対するPCI Expressの導入には、レガシィPCIの性能限界という背景があった。したがって、PCI ExpressでMFPの画像データの同期転送に要求される性能を達成できるか、性能面の実力値をいち早く把握することが重要課題のひとつとなった。しかし、パラレル通信方式からシリアル通信方式への転換に伴い、物理層信号の伝送レートは向上する反面、レイテンシの増大が避けられない。また、PCIに比べて設計パラメータも飛躍的に増加しており、各設計パラメータ同士が相互に依存し合うことで、データ転送性能が大きく変化してしまう。そのため、組み込むシステムで必要とされる同期転送制約にマッチした設計パラメータを選択しないと、システム全体としての性能が、従来のPCIよりも低下する可能性がある。

上記のように、PCI Expressを採用したシステムは、複雑な設計要素が影響し合うため、静的な机上計算でシステム性能を正確に予測することは困難である。このため、シミュレーションによる動的な解析で定量的にPCI Expressの性能を評価して、設計の上流工程で基本通信特性を把握する必要がある。

## 2. 技術

### 2-1 ハードウェアモデリング手法によるPCIe性能予測モデル

#### 2-1-1 ハードウェアのモデリング手法

ハードウェア設計前の上流工程の段階ではRTL (Register Transfer Level) の回路設計データはまだ存在せず、性能予測向けのシミュレーションモデルを独自に開発する必要がある。ハードウェアのモデル化は抽象度の高いシミュレーションでシステム動作を確認する手法で、複雑なシステムを設計する際に用いられている。ハードウェア設計前の上流工程の段階で、動作解析しながら大きな問題点をつぶし、間違いの無い実装設計の指針をたてられる。近年のシステムレベル設計<sup>2),3)</sup>では記述が簡単なC言語ベースのハードウェアモデルが主流となっており、HDL (Hardware Description Language) よりも記述量が少なく、シミュレーションの実行速度が速い、という特徴がある。特に、出来るだけ抽象度の高いモデルで、簡単かつ正確なものであるほど設計上流におけるシステム設計検証／修正が短期間で可能になる。

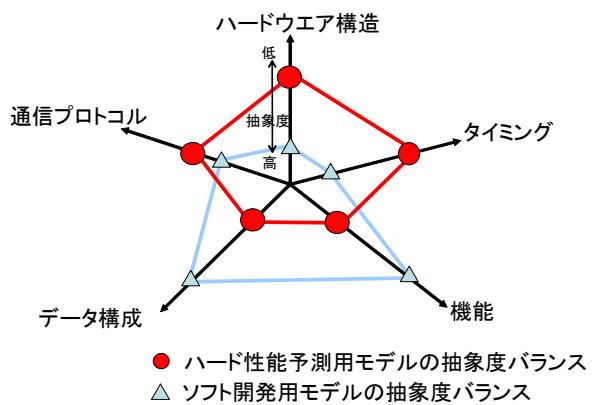

Fig.2は、ハードウェアモデルの抽象度のバランスを5つの設計要素の軸で表現したグラフである。グラフの中心ほど各要素の抽象度が高いことを示しており、中心からもっとも離れた点が、回路記述がまったく抽象化されていないRTL設計データに相当する。

それまで多く利用されていたソフトウェアとの協調設計を目的としたモデルの抽象度を、Fig.2のグラフでは三角の点で示した。ソフトウェアに対する動作を検証する事を目的としているために、機能とデータの構成は詳細に記述し、構造やプロトコルについては抽象度が高くなっている。PCI Expressのハードウェア性能予測には、構造・タイミング・通信プロトコルといった、それまでのモデルで抽象度が高かった設計要素の影響を再現できることが不可欠である。そこで、我々は新たにFig.2の丸の点で示した抽象度のバランスのモ

デリングスタイルを考案した。ハードウェアの構造を詳細化することで、性能を見積もる際に不可欠な要素となるタイミング情報を正確に表現することができる。逆に、各モジュールの機能やデータ構成の抽象度を上げることでシミュレーションの時間をできるだけ短縮できるようにした。言い換えると、“効率の良い動作予測可能なブロック図”となっている。

Fig.2 Balance Chart of Abstraction Level.

#### 2-1-2 PCIe性能予測モデルの開発

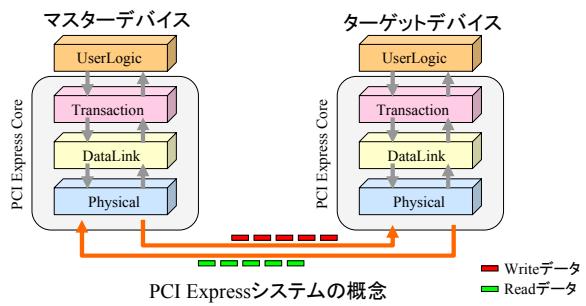

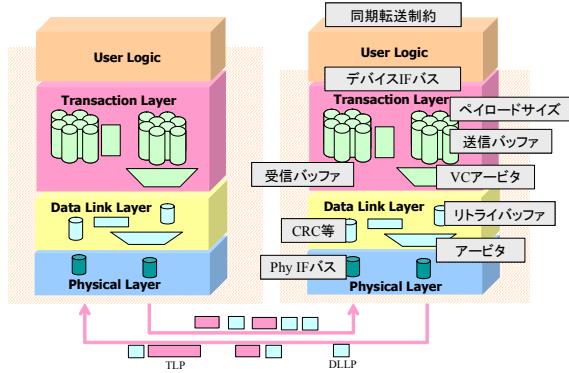

PCI Expressのハードウェアモデルでは、MFPの画像データバスを想定した性能予測に利用するため、通信コア単体ではなく、画像機器に要求される画像データの同期転送制約をもった、対向通信システム全体をモデル化した。また、シミュレーション精度はパケット単位の精度を目標とした。Fig.3にPCI Expressによる画像データ通信システムモデルの概念図を示す。マスターデバイスとターゲットデバイスをPCI Expressで接続して画像データを相互にやりとりするもので、PCI Express通信コアの部分は、Transaction レイヤー、DataLink レイヤー、Physical レイヤーの3つのレイヤーで構成される。2つのデバイス間が送受信用の2本のシリアル線でつながれており、スキャナ画像データ(Writeデータ)、プリンタ画像データ(Readデータ)をはじめとする画像データパケットと、PCI Express規格で規定されるDLLP (Data Link Layer Packet) 等の通信プロトコルを管理するための制御パケットが双方向に転送される。

Fig.3 PCI Express Data Transfer System Concept.

モデルの作成にあたり、PCI Expressの仕様からデータ転送レートに影響を及ぼす重要な機能および設計パラメータを抽出した。モデルに実装した機能および設計パラメータを以下に示す。

- ・ レーン数およびVC (Virtual Channel) 数

- ・ FC (Flow Control) 制御動作

- ・ タイムアウト、エラーによる再送動作

- ・ VCアービトレイション・データリンク層アービトレイション動作

- ・ 送受信バッファサイズ・リトライバッファサイズ

- ・ バス帯域、遅延発生パターン

- ・ 各種解析用ログの出力

特に重要な機能は、PCI Expressの規格上実装依存度が高い設計パラメータである。たとえば、制御パケットの発行周期や、パケットを格納する内部バッファの構成およびデータリンク層のアービトレイション（パケット転送が競合した際の優先度調停）方式などは、搭載するシステムの用途に合わせて最適な実装方式を決定する必要がある。

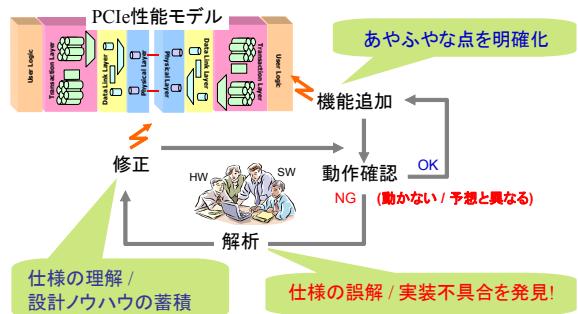

モデル化を進める過程をFig.4に示す。モデルに新しく機能を追加する際は、コーディングできるレベルまで動作を理解できていなければならない。この時点で機能仕様のあやふやな部分が浮き彫りになり、再検討することで明確化される。追加した機能は、シミュレーションによって動作を確認し、問題が無ければ次の機能追加へ進む。しかし、実際には動かなかつたり、

予想と異なる動作をしたりする問題が生じる場合がある。この時点で再度シミュレーション結果を解析することで、仕様の誤解やモデルへの実装の不具合を発見する。モデルの修正あるいは仕様の誤解を正して動作確認するごとに、仕様の理解度と設計上のノウハウが蓄積し、複雑な仕様書を読んだだけでは誤解していた部分が、正しいものへと修正されていく。この作業を繰り返してモデルを詳細化する。短期間で設計パラメータの理解度を効率良く高めることができることは、ハードウェアモデリング手法の効果のひとつである。

Fig.4 Hardware Modeling Process.

コーディングの完了したモデルには、各機能の性能値をパラメータとして埋め込んでいく。Fig.5にPCI Expressの通信性能に影響を与える要素を示す。デバイスのUser Logicからは、画像データ転送に同期したタイミングで、データ転送要求のコマンドが発行される。Transactionレイヤーでは、VC (Virtual Channel) とよばれる複数の仮想的な通信チャンネルが定義され、それぞれが送受信のためのパケットバッファメモリを持ち、さらにアービタによるトラフィック制御でQoS (Quality of Service) を実現する仕組みが用意されている。Data Linkレイヤーでは、Physicalレイヤーの通信を保証するための制御パケットの生成やエラー検出などの管理、再送処理用のリトライバッファなどの仕組みを持っている。また、これら制御用のパケットと Transaction レイヤーから発行されるMemory Readや Memory Writeなどのトランザクション用のパケットとのアービトレイションなども処理されている。さらに、内部バスIF (Interface) の帯域も実装条件に合わせて

考慮する必要がある。これらの要素の実装方式に合わせて性能値をパラメータ化し、機能モデルに性能値を埋め込むことで、PCI Express性能予測モデルを完成させた。

Fig.5 Parameters for Performance Estimation.

## 2-2 PCIe性能予測モデルによる通信特性評価

### 2-2-1 単一トラフィックの通信特性

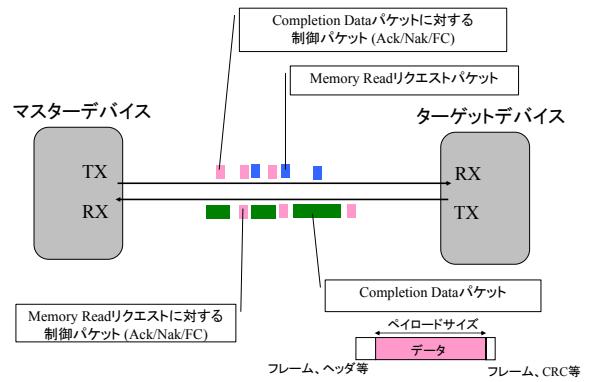

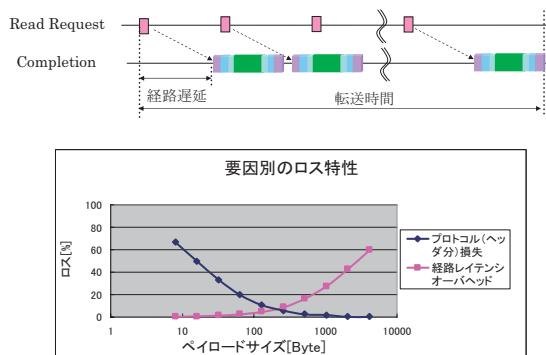

初めに単純な通信特性として、PCI ExpressのMemory Readのデータ転送レートを測定した結果を示す。Memory Read転送ではFig.6に示すように、マスターデバイスからのMemory Readリクエストと、ターゲットデバイスからは、Memory Readリクエストで要求されたデータを応答するCompletion Dataパケットおよびそれぞれのパケットに対するAck (Acknowledge) / Nak (Negative Acknowledge) 通知パケットやFC (Flow Control) 制御パケットが双方向に転送される。Completion DataパケットはFig.6に示すように、データ領域とそれ以外のフレームやヘッダの領域とから構成される。またデータ領域の大きさをペイロードサイズと呼ぶ。

Fig.6 Example of Memory Read Transaction.

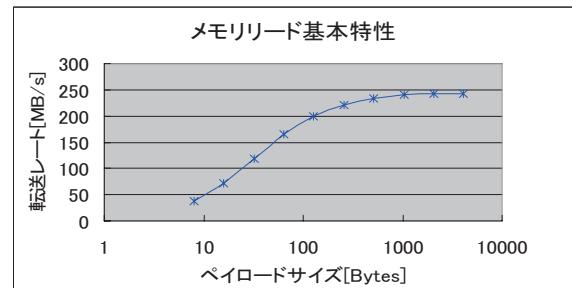

Fig.7のグラフに、PCI Express × 1 レーン接続時のMemory Read転送における、ペイロードサイズ特性を測定した結果を示す。測定条件として、バッファサイズには制限を与えず十分に大きくし、Memory Readリクエストを連続させた。× 1 リンクの理論限界転送レート250MB/secに対して、ペイロードサイズが小さいと、プロトコルオーバヘッド（パケットを構成するヘッダサイズとペイロードサイズの比率や制御パケット数の増大）によって、大きくデータ転送レートが低下することが分かる。このため単純なデータ転送では、ペイロードサイズを大きくする必要がある。

Fig.7 Payload Size vs Memory Read Performance.

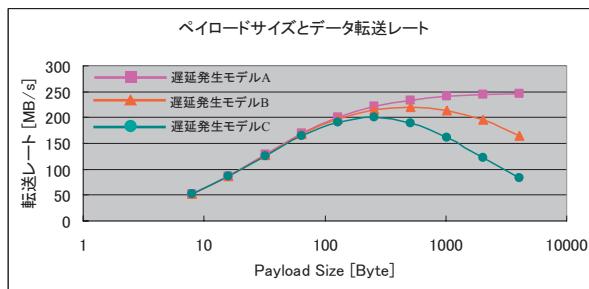

次に、マスターデバイスからMFPシステムの画像データ転送に固有の同期制約を加え、PCI Express通信コア内部の遅延発生モデルを3通り（A, B, C）に変えた場合のペイロードサイズとデータ転送レートの特性を確認した。結果をFig.8のグラフに示す。遅延モデルBおよびCでは、ペイロードサイズが大きすぎると性能が低下し、Fig.7のグラフの結果に反する特性があるこ

とがわかった。これは、同期転送の制約条件として与えた、1周期あたりの画像データの転送サイズとMemory Readリクエストが送信されてからCompletion Dataパケットを受信するまでに要する経路の遅延によって発生するオーバーヘッドおよびパケットのペイロードサイズとヘッダサイズの比率による損失のバランスが影響するためである。

Fig.8 Payload Size vs Memory Read Performance.

Fig.9に画像データの転送時間と経路遅延の関係を示したタイミングチャート（上図）および経路で発生する遅延の影響によるデータ転送レートのロスおよびヘッダサイズによるプロトコル損失のロスの要因別のロス特性に書き直したグラフ（下図）を示す。Fig.9のグラフのシミュレーション結果から、ペイロードサイズを128B~256Bにすると双方のロスが小さい効率の高いデータ転送が可能といえる。画像データの同期転送制約の下では、回路実装方法によって変わる経路遅延時間と、プロトコルロスを考慮した、適切なペイロードサイズの選択が必要であることがわかった。

Fig.9 Payload Size vs Protocol Overhead and Latency Overhead.

## 2-2-2 複合トラフィックの通信特性

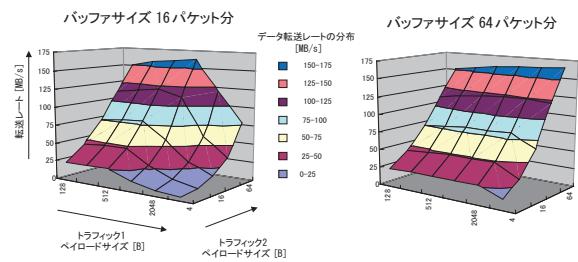

複合トラフィックの通信特性を評価した例として、Fig.10に2つのデバイス間で、双方向に2つのトラフィックを発生させたときのバッファサイズ等の特性を示す。それぞれのグラフの縦横軸は2つのトラフィックで使用するデータパケットのペイロードサイズの組み合わせで、高さが転送レートを表している。左右のグラフは、PCI Express通信コアの内部バッファサイズについて、16パケット分と64パケット分の大小2種類を比較したものである。バッファサイズが64パケット分確保されている場合は、大きいペイロードサイズの組み合わせによって高いデータ転送レートが得られるが、バッファサイズを16パケットに制限した場合は高いデータ転送レートが得られるペイロードサイズの組み合わせの範囲が限定されることがわかった。このようにトラフィック数とパラメータの組み合わせが増えてくると静的な解析は困難となり、モデルによる動的な解析が有効となる。

Fig.10 Buffer Size and Payload Size of Bi-Direction Traffic.

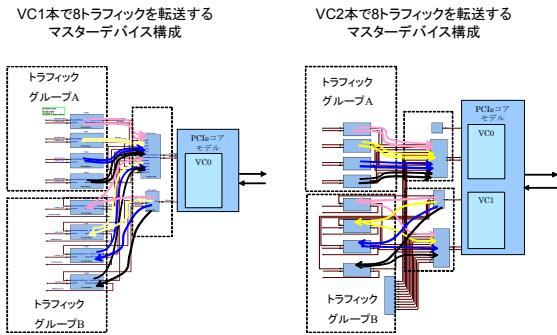

さらに複雑な例として、Fig.11にPCI ExpressのVC（Virtual Channel）を利用して、2つのトラフィックグループ（A, B）に分けられた複合トラフィックを転送するマスターデバイス構成を示す。ここでトラフィックグループAは4本のスキャナ画像入力であり、トラフィックグループBは4本のプリンタ画像出力である。従って同時に発生するトラフィックは最大8本となり、しかも各トラフィックのペイロードサイズや使用するVCの数とバッファサイズが異なった通信条件をとることができ。このような複雑な通信システムの性能は

机上計算が不可能となり、回路設計を始める前の設計上流工程ではモデルで性能を予測する手法が有効である。

Fig.11 Simultaneous Traffic using Virtual Channel.

### 3. 成果

#### 3-1 ハードウェアモデリング手法によるPCIe性能予測の効果

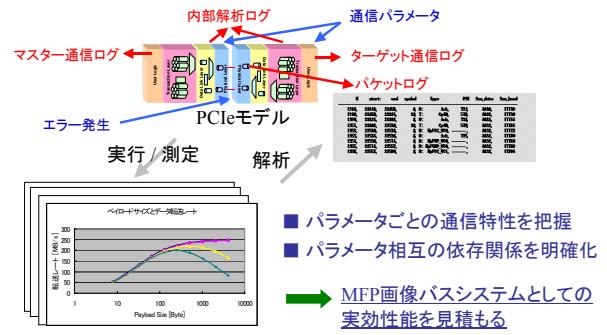

基本通信特性評価の流れをFig.12にまとめる。システムモデルには、解析用にマスターデバイスおよびターゲットデバイスの通信ログ、プロトコル解析に利用するパケットログさらには内部動作解析ログの出力機能を設けている。また外部から入力する情報として、PCI Expressの通信パラメータや内部ブロックの処理に与える遅延、エラーの発生頻度などを任意に指定することができる。この環境を利用してシミュレーションを実行することで、通信特性を測定することができた。予想と異なる結果などが得られた場合は、各種のログデータやシミュレーション中のモデル内部の動作を解析することによって、なぜそのような特性になるか、影響を与える通信パラメータに対する変化などを解析する。このような評価を通信条件を変えながら進めいくことで、PCI Expressの基本的な通信特性を把握し、設計パラメータの依存関係を明確化した。MFP画像バスシステムとしての実効性能をRTLや実機の無い段階の設計上流工程で見積もることができた。

Fig.12 Process of PCIe Performance Estimations.

#### 3-2 PCIe IP導入に対する性能予測結果の反映

基本特性評価シミュレーションの実施結果は、その後の設計工程において製品開発向けに導入するPCI Express IP (Intellectual Property) コアの選定に活用している。性能予測モデルで評価した結果をもとに、性能面に着目したIPチェックリスト (Table 1) を作成し、性能面で留意した部分の仕様に問題が無いことを確認した。

Table 1 PCIe IP Checklist.

| チェックポイント        | 判定結果 |

|-----------------|------|

| VCアービトリエーション    | ○    |

| Ordering機能      | ○    |

| FCアルゴリズム        | ○    |

| FCパラメータ         | ○    |

| Link層アービトリエーション | ○    |

| FC, Ack/Nak通知方式 | ○    |

| 送信バッファ          | ○    |

| リトライバッファ        | ○    |

| 受信バッファ          | ○    |

さらに、導入したIPをカスタマイズして評価チップを開発する際にも、ハードウェアモデルによる評価結果を参照して実装仕様を決定した。完成したハードウェアによる実測値とシミュレーションの結果は、基本的なDMA (Direct Memory Access) 転送のデータ転送レートにおいて、差異が約0.2%であり、開発したモ

モデルが高い精度で実機の性能を予測できることを確認できた。

## 4. 今後の展開

本稿では性能予測用PCI Express通信コアモデルによるデータ転送性能評価を題材に、ハードウェア性能予測向けモデリング手法の適用効果を報告した。PCI Express IPコアの導入に先駆けて、モデルによる最適な各種パラメータ検討を開始し、RTLや実機が無い段階からシステム性能評価まで実施できた。ハードウェアモデリング手法適用の効果として、モデル化（動かすこと）を通じて仕様理解度が深まり、複雑な通信パラメータが性能に及ぼす影響を早期に把握することができた。またIP選定を想定したチェックポイントを事前に明確にできたことも、デジタルカラーMFPにおけるPCI Expressのスムーズな導入に繋がった。

本手法は、現在までにMFPのコントローラ制御チップの内部設計などにも適用範囲を広げ、大規模なシステムレベル設計の効率化に貢献している。近年はOSCI (Open SystemC Initiative) によるTLM (Transaction Level Modeling) 規格の標準化をはじめとするシステムレベル設計における性能予測向けモデリング技術の進歩や、IPベンダーからハードウェア性能予測に利用可能なCモデルが提供される事例も見受けられ、さらなるモデルの開発工数削減が期待される。今後もこれらのシステムレベル設計の効率化につながる技術を取り込み、より簡単で精度の高い動作解析シミュレーション技術を確立していきたい。

## 参考文献

- 1) PCI-SIG: PCI Express Base Specification Revision 1.0, (2002)

- 2) Thorsten Grötker, et al.: SystemC によるシステム設計, 丸善, (2003)

- 3) Daniel D. Gajski, et al.: SecC 仕様記述言語と方法論, CQ 出版社, (2000)

注1) PCI-SIG, PCI, PCI Express および PCIe はPCI-SIG の登録商標です。

注2) OSCI および SystemC は Open SystemC Initiative の登録商標です。