# FIBによるULSI回路修正時の帯電防止技術の開発

## Antistatic Techniques for Suppressing Charging in FIB-SEM Combined System

薦田 弘敬\* 森谷 千恵\*

Hirotaka KOMODA Chie MORITANI

### 要　　旨

FIB (Focused Ion Beam) によるULSIの回路修正（内部配線のつなぎ替え）は、ULSIデバイス開発時のデバッグに用いられ、マスク改訂回数の低減に多大な寄与をしている。しかし、アナログデバイスに代表される製品では、イオンビーム照射による帶電が原因で生じるESD (Electrostatic Discharge) 破壊、デバイス特性シフトが重要な問題となっている。そこで、われわれはFIB-SEM複合装置を用いた3つの帶電防止技術を開発した。本報告では、今回開発した3手法の帶電防止効果および帶電防止機構を各種実験結果から明らかにし、それぞれの特徴を示す。さらに、帶電によるデバイス特性シフトを防止した状態で、同一装置内の各種アナログ／ロジックデバイスの効率的な回路修正を実現するため、デバイス・加工条件の種類に最適な3手法の使い分けを提示する。

### ABSTRACT

Focused ion beam (FIB) technologies are now routinely used for circuit modifications during the debugging phase of ULSI development. However, FIB-induced charging causes electrostatic discharge (ESD) damage and changes transistor parameters. Thus, for ULSI makers, achieving successful circuit edit without the FIB-induced charging is one of the most critical issues to reduce the development costs and time-to-market of new devices. We have developed three antistatic techniques for suppressing the FIB-induced charging in a FIB-SEM combined system. In this paper, the effectiveness and mechanism of our antistatic techniques were investigated and discussed. We also proposed an application criterion of the three methods to realize successful and efficient circuit edits of various devices without FIB-induced charging in the same FIB-SEM combined system.

\* 電子デバイスカンパニー 品質保証部

Quality Assurance Department, Electronic Devices Company

## 1. 背景と目的

FIB (Focused Ion Beam) によるULSIの回路修正は、FIBの3機能（見る、切る、貼る）を活用しULSI内部配線のつなぎ替えを行うもので、ULSIデバイス開発時のデバッグに用いられ製品開発に多大な寄与をしている<sup>1)</sup>。しかし、イオンビーム照射による帶電が原因で生じるESD (Electrostatic Discharge) 破壊、デバイス特性シフトが回路修正時の大きな課題となっており<sup>2), 3)</sup>、帶電防止技術の開発が切望されている。それにもかかわらず、FIB装置に搭載された帶電防止技術としてこれまでに公表されているものは電子シャワー<sup>2), 4)</sup>のみである。さらに、電子シャワーを用いる際の最適条件については経験的なものしかなく、周辺デバイスへの悪影響についても十分評価されていない。このようにFIBの帶電防止技術に関する研究は非常に少ないのが現状である。

以上の背景に鑑み、電子シャワーに替わる新たな帶電防止技術の開発を行った。本開発においては、アナログデバイスとロジックデバイスの回路修正時に用いられるFIB加工条件の違いを考慮し、両デバイスの回路修正に適用可能な帶電防止技術を同一装置内で実現することを目標とした。次章以降ではまず、本研究に用いたFIB-SEM複合装置の概要を述べる。次に、今回開発した3つの帶電防止技術の詳細を述べ、デバイス・加工の種類に最適な手法の使い分けを提示する。

## 2. FIB-SEM複合装置

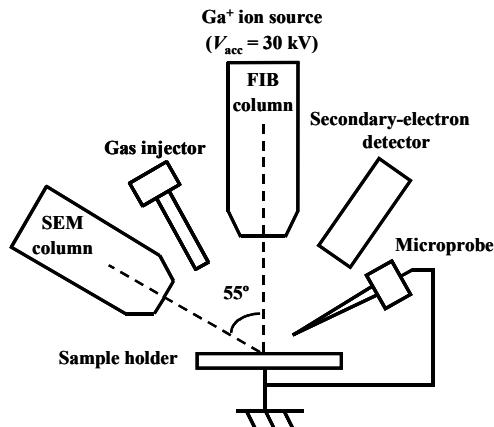

エスアイアイ・ナノテクノロジー製FIB-SEM複合装置SMI2050MS2およびSMI3050SEを用いた。装置の模式図をFig.1に示す。FIBの加速電圧は30kVで、0.1μm以下に絞ったGa<sup>+</sup>イオンビームを加工領域内でスキャンする。SEM鏡筒はFIB鏡筒と55°の角度で搭載されている。また、マルチガスシステムにより、FIBデポ機能およびGAE (Gas Assisted Etching) 機能を有する。試料傾斜範囲は-3～60°である。今回の実験では、SMI3050SEにマイクロプローピングシステムを搭載した。GNDに接続されたタンゲステン製マイクロプローブ（先端径：約1μm）をSEM像でモニターしながらnm

レベルの精度で位置制御可能である。

Fig.1 Schematic diagram of FIB-SEM combined system.

## 3. 500eV収束電子ビームを用いた帶電中和技術

従来技術の電子シャワーでは多量の電子をcmオーダーの広範囲に照射するため、FIB加工領域以外の周辺デバイス特性を変化させてしまう問題がある。電子を用いた帶電中和技術では、中和に最適な量の低エネルギー電子をFIB加工領域のみに供給することが重要である。そこで、FIB-SEM複合装置のSEMをチャージニュートラライザーとして用いることで、この課題を解決することを試みた<sup>5)</sup>。本手法では、加速電圧500Vでビーム径約50μmに絞った電子ビーム (FEB : Focused Electron Beam) をFIB加工領域に同時照射する。

### 3-1 サンプルおよび実験手順

±12Vを超える電圧がコントロールゲート (CG) に印加されれば閾値電圧 ( $V_{th}$ ) シフトとして検出可能である EEPROM (Electrically Erasable-Programmable Read-Only Memory) デバイスを用いて、FIB, FEB照射により生じる帶電電位を評価した。実験に用いたサンプルは、ゲート長0.6μm, 2層メタルプロセスで製造されたウェーハ状態のEEPROM単体セルである。約250μm間隔で配置された3個のEEPROM単体セルのうちフローティング状態にあるCGパッド電極の1つにFIB,

FEBを照射し、その際生じる試料表面の帶電電位を評価した。FIBはCGパッド電極上の $20 \times 20 \mu\text{m}^2$ 領域を走査した。FIB, FEBの照射時間は全て300秒である。

### 3-2 FEB照射による帶電電位

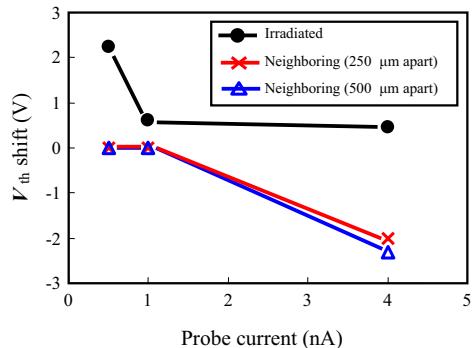

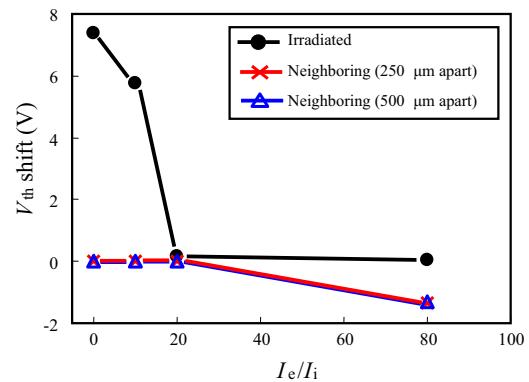

まず、今回チャージニュートラライザーとして用いたFEBのみを照射した際に生じる帶電電位を評価した。照射デバイスおよび周辺デバイスの $V_{th}$ シフト量のFEBプローブ電流 ( $I_e$ ) 依存性をFig.2に示す。FEBにより照射されたEEPROMデバイスの $V_{th}$ はプローブ電流量に関わらずプラスにシフトしているのに対し、その周辺（距離 : 250μm, 500μm）デバイスでは $V_{th}$ シフトは無視できるレベルか、もしくはマイナスである。この $V_{th}$ シフト量からFEBにより照射されたEEPROMデバイスのCGパッド電極は $I_e = 0.5\text{nA}$ の時は約15V,  $I_e = 1\text{nA}$ および $4\text{nA}$ の時は約13Vプラスに帶電していると判断できる。一方、その周辺デバイスのCGパッド電極の帶電電位は $I_e = 0.5\text{nA}$ および $1\text{nA}$ の時は±12V以下であるが、 $I_e = 4\text{nA}$ の時は約16Vマイナスに帶電していると判断できる。

Fig.2  $V_{th}$  shifts of irradiated and the neighboring (250μm and 500μm apart from the irradiated device) EEPROM devices as a function of FEB (500 eV) probe current.

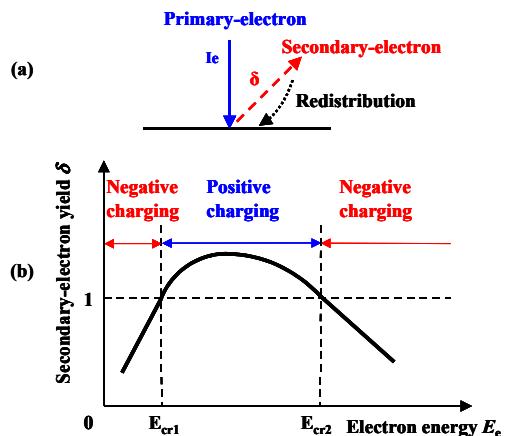

上記の結果を説明するために、電子ビーム照射時の試料帶電を二次電子放出およびその再配分を用いて考察する (Fig.3(a)参照)。放出された二次電子が再び試料表面に引き戻される場合、それを二次電子の再配分と呼ぶ。二次電子放出率 ( $\delta$ ) は電子ビームの照射条件（電子エネルギー ( $E_e$ )、照射角度）により大きく変化し、 $E_e$ と $\delta$ との関係はFig.3(b)のようになる<sup>6)</sup>。 $0 < E_e <$

$E_{cr1}$ 、または $E_{cr2} < E_e$ の場合、 $\delta < 1$ であることから試料はマイナスに帶電し、帶電電位 ( $V_p$ ) はそれぞれ $V_p = -E_e / q$ ,  $V_p = -(E_e - E_{cr2}) / q$ で飽和する。ここで $q$ は素電荷である。一方、 $E_{cr1} < E_e < E_{cr2}$ の場合は、 $\delta > 1$ であることから試料はプラスに帶電し、その試料表面近傍には二次電子放出に対して減速電界が発生し二次電子の再配分を引き起こすため、試料の帶電電位は10数V以下に抑えられ安定する。

Fig.3 (a) Emission and redistribution of secondary-electron and (b) dependence of secondary-electron yield on electron energy for electron beam irradiation.

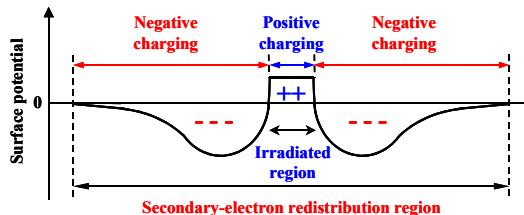

電子ビームをチャージニュートラライザーとして用いる場合、電子ビーム照射による帶電電位を最小限に抑えるためには10eV以下、あるいは $E_{cr1}$ ,  $E_{cr2}$ 近傍のエネルギーを用いるのが理想である。しかし、一次電子として10eV以下の低エネルギー電子をFIB加工領域に供給する場合、空間電荷制限により中和に必要な量の電子を供給できない可能性がある。また、 $E_{cr1}$ ,  $E_{cr2}$ の値は試料の組成や表面状態、試料傾斜角などにより異なる。したがって、電子ビーム照射による帶電電位を最小限に抑える現実的な解決策の1つとして、本装置のチャージニュートラライザーではプラス帶電条件 ( $\delta > 1$ ) の電子ビームを用いている。 $\delta > 1$ の電子ビーム照射の場合、照射領域およびその周辺部の帶電電位分布は二次電子再配分により決まり、Fig.4に示すような分布になる<sup>7)</sup>。本実験の場合は、FEBの一次電子により照射されたEEPROMデバイスのCGパッド電極はプラスに

帶電し、その周辺デバイスのCGパッド電極は二次電子の再配分によりマイナスに帶電していると考えられる。その結果、FEBにより照射されたEEPROMデバイスの $V_{th}$ はプラスにシフトし、その周辺デバイスの $V_{th}$ はマイナスにシフトする (Fig.2)。

Fig.4 Illustration of surface potential distribution on insulator for electron beam (secondary-electron yield  $\delta > 1$ ) irradiation.

### 3-3 FEB照射による帶電中和効果

次に、今回チャージニュートライザーとして用いたFEBをFIBと同時にフローティング状態にあるCGパッド電極に照射した際の帶電中和効果を評価した。その結果をFig.5に示す。FEB電流とFIB電流 ( $I_i$ ) の比 ( $I_e / I_i$ ) をパラメータとし、 $I_i = 50\text{pA}$ 一定で $I_e$ を0から4nAまで変化させた。FIBのみ照射した場合 ( $I_e / I_i = 0$ ) は、照射デバイスの $V_{th}$ シフトは7.4Vであるのに対し、その周辺デバイスでは無視できるレベルである。この結果より、FIBにより照射されたデバイスのCGパッド電極は約20Vプラスに帶電しているが、その周辺デバイスの帶電電位は±12V以下であると判断できる。これに対し、FEBをFIBと一緒に照射した場合は、照射デバイスと周辺デバイスの $V_{th}$ シフト量は $I_e / I_i$ に依存する。照射デバイスの $V_{th}$ シフトは $I_e / I_i = 10$ の時はプラスであるのに対し、 $I_e / I_i = 20$ および80の時は無視できるレベルである。一方、周辺デバイスの $V_{th}$ シフトは $I_e / I_i = 10$ および20の時は無視できるレベルであるのに対し、 $I_e / I_i = 80$ の時はマイナスである。

Fig.5  $V_{th}$  shifts of irradiated and the neighboring (250μm and 500μm apart from the irradiated device) EEPROM devices as a function of probe current ratio ( $I_e/I_i$ ) of electron (500eV) to ion (30keV) beam. The probe current  $I_i$  of ion beam was kept at 50pA.

これらの結果は以下のように説明することができる。FIBのみ照射した場合 ( $I_e / I_i = 0$ )、二次電子、二次イオン、中性粒子が放出されるが、加速電圧が30kVの場合Ga<sup>+</sup>イオン1個に対して二次電子は数個放出されるのに対し、二次イオンはその1/10程度しか放出されない。その結果、プラスのイオンが打ち込まれマイナスの電子が放出されることになるためFIB照射時には試料表面は必ずプラス帶電する。一方、FEBをFIBと一緒に照射した場合は、これらの照射により生じた二次電子の低エネルギー成分がビーム照射によるプラス帶電を中和するのに重要な役割を果たしていると考えられる。 $I_e / I_i = 10$ の時は、このプラス帶電を中和するのに十分な低エネルギー二次電子を供給しきれないため照射デバイスの $V_{th}$ はプラス側にシフトしている。一方、 $I_e / I_i = 80$ の時は多量の低エネルギー二次電子がビーム照射領域に供給されているためビーム照射によるプラス帶電を中和できるが、二次電子の高エネルギー成分は周辺部に再配分され、その領域をマイナス帶電させてしまう。その結果、照射デバイスの $V_{th}$ シフトは無視できるレベルであるが周辺デバイスの $V_{th}$ はマイナス側にシフトしてしまう。Fig.5よりビーム照射による帶電を中和し、かつ周辺デバイスにも影響を与えない最適条件は $I_e / I_i = 20$ の時にほぼ得られていることがわかる。この条件の時には、ビーム照射による帶電を中和するのに必要な

最適量の低エネルギー二次電子が供給されていると考えられる。

## 4. マイクロプロービングおよびFIBデポ機能を用いた帯電防止技術

前章で述べた500eV FEBチャージニュートラライザーを最適条件で用いることにより、付加時間ゼロで帶電に敏感なアナログデバイスの回路修正をデバイス特性の変動なしに実施することが可能になった。しかし、今回用いたFIB-SEM複合装置のFEBの最大プローブ電流が10nAであることから、最適条件を満足するFIBの最大プローブ電流は500pAに制限されている。さらに、大電流の電子ビーム照射の際には多量の二次電子による周辺デバイスへの悪影響も懸念されるため、nAレベルの大電流FIB加工に対しては電子ビーム以外の帶電防止技術の開発が必要である。そこで、大電流FIB加工を対象としFIB-SEM複合装置に搭載したマイクロプロービングシステムおよびFIBデポ機能を組み合わせることで、FIB照射による帶電電荷をGNDへ逃がす電流経路を容易に形成する技術（以下、本技術をマイクロプローブ+FIBデポ法と呼ぶ）を開発した<sup>5),8)</sup>。

### 4-1 マイクロプローブ+FIBデポ法

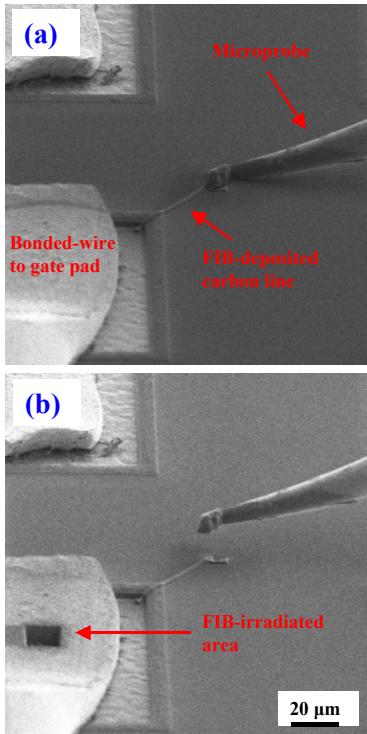

評価用デバイスには、24pin-DIP（Dual Inline Package）にパッケージングしたNMOS（N-channel MOS）トランジスタ（ゲート長0.35μm, 3層配線プロセス）を用いた。ソース、ドレイン、基板、ゲートパッドはそれぞれのパッケージpinにAlワイヤで接続されている。ゲートのみをフローティングにし、他の電極はGNDに接続した状態で、ゲートパッドとマイクロプローブ（GND電位）とをFIBカーボンデポ膜にて接続した場合としない場合について、ゲートパッドにFIB照射した際のソース・ドレイン間電流（I<sub>d</sub>）-ゲート電圧（V<sub>g</sub>）特性シフト量を比較した。実験手順を以下に示す（Fig.6参照）。

- (1) マイクロプローブのタッチダウン：試料法線から55°の方向から低加速・少電流の高分解能SEM像にてモニタリングしながら、FIB加工箇所近傍に

マイクロプローブをタッチダウンさせる。そのため、プローブが試料表面に接触したかどうかの確認が容易であり、かつビーム照射による帶電を最小限に抑えることができる。

- (2) FIBカーボンデポ：まず、マイクロプローブとFIBデポ膜との電気的接觸を確実にとるため、マイクロプローブ先端を含む $5 \times 5\mu\text{m}^2$ 領域にI<sub>i</sub> = 300pAで133秒間（厚さ約0.5μm）カーボンをデポした。その後、さらなるカーボンデポによりカーボン膜とフローティング状態にあるゲートパッドとを接続し、ゲートパッドからGND電位のマイクロプローブへの電流経路（幅：1.5μm, 長さ：40μm, 抵抗値：20MΩ狙い）を形成した。デポ時間はI<sub>i</sub> = 300pAで200秒であった。FIBカーボンデポ後のSEM写真をFig.6(a)に示す。

- (3) FIB照射：ゲートパッドのワイヤーボンド部 $10 \times 10\mu\text{m}^2$ 領域を、I<sub>i</sub> = 6.9nAで120秒間走査した。

- (4) マイクロプローブのリフトオフ：マイクロプローブと接続されたFIBカーボンデポ膜をFIB加工によりカットする必要がなく、SEMでモニタリングしながらマイクロプローブを引き上げればよいため、ビーム照射による帶電を最小限に抑えることができ所要時間は数秒である。リフトオフ後のSEM写真をFig.6(b)に示す。

Fig.6 Scanning electron micrographs showing procedure of microprobing and FIB-assisted deposition method: (a) after touchdown of microprobe on sample surface and FIB deposition to form carbon line which makes current path from gate pad to microprobe (GND) and (b) after FIB irradiation to bonded-wire to gate pad of NMOS transistor and lift-off of microprobe.

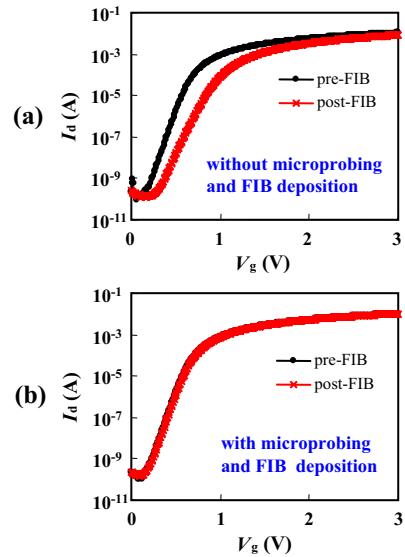

#### 4-2 マイクロプローブ+FIBデポ法の帯電防止効果

Fig.7にFIB照射前後のNMOSトランジスタの $I_d - V_g$ 特性を示す。本手法適用なしの場合 (Fig.7(a)) は、FIB照射によりサブスレショルド係数 ( $S$ ) および $V_{th}$ がそれぞれ29mV/decade, 220mV高い側へシフトした。それに対し、本手法を適用した場合 (Fig.7(b)) は、 $S$ および $V_{th}$ シフトをそれぞれ、FIB照射していないリフアレンスデバイスと同等の1.5mV/decade, 10mV以内に抑えることができた。本実験においては、フローティング状態にあるゲートパッドにFIBを照射しているため、ゲート電位が上昇しゲート酸化膜へのホットキャリア注入が生じる。これらのホットキャリアはゲート酸化膜中や界面に電気的な欠陥準位を形成し負のトラップ電荷を生じるため、 $S$ および $V_{th}$ がプラス側へシフトす

る。本手法適用時は、フローティング状態にあるゲートパッドがプローブおよびFIBカーボンデポ膜によりGNDに接続（数10MΩ）されているため、FIB照射による電圧上昇を抑えることができトランジスタ特性シフトが防げたと考えられる。

Fig.7 Pre- and post-FIB  $I_d$  vs  $V_g$  curves of NMOS transistors for FIB probe current of 6.9 nA: (a) without or (b) with micropointing and FIB-assisted deposition method.

## 5. 試料傾斜加工によるESD破壊防止技術

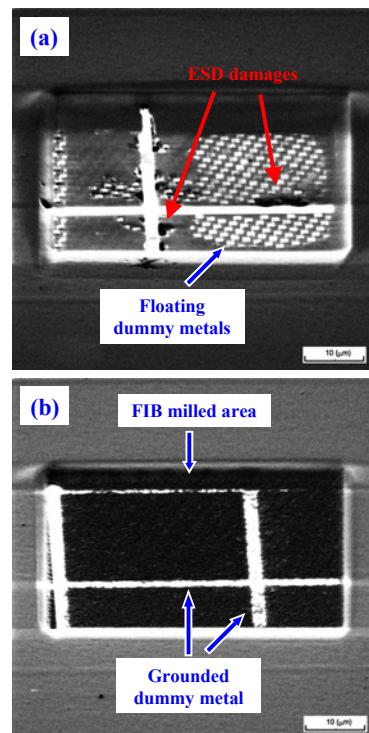

ロジックデバイスの回路修正においては、FIB加工穴のアスペクト比を下げるため上層膜を数10μm角で除去する必要があり、nAオーダーの大電流GAEが用いられることがしばしば生じる。このような大電流加工時に生じるESD破壊を防止することが回路修正を成功させるキーになっている。われわれは、試料を傾斜させた状態でFIB加工を行うことでESD破壊が防止できることを見出した<sup>9)</sup>。本章では、試料傾斜加工のESD破壊防止効果を実験により示し、本手法のESD破壊防止メカニズムを考察する。

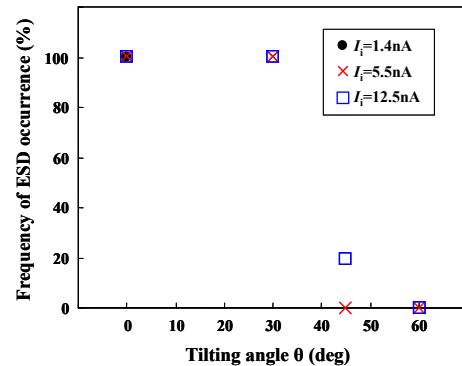

## 5-1 試料傾斜加工のESD破壊防止効果

評価用デバイスには、ゲート長0.13μm, 8層Cu配線プロセスのロジックLSIを用いた。本デバイスは、CuデュアルダマシンおよびCMPプロセスを採用しているため、パッシバーション膜厚はチップ内で均一である。実験ではサンプルの任意箇所のパッシバーション膜50×50μm<sup>2</sup>領域を最上層Cu配線が露出するまでFIB加工し、その過程でESD破壊が発生するかどうかにより各実験条件の効果を評価した。

Fig.8にXeF<sub>2</sub> GAEを実施した際の試料傾斜角(θ)とESD破壊発生頻度との関係を示す。各実験条件に対して5回加工を行った。試料傾斜角が0°の場合は、プローブ電流が1.4nAにおいても100%ESD破壊が生じるのに対し、60°にすることでプローブ電流12.5nAに対してもESD破壊を防止できることがわかる。Fig.9に、0°および60°傾斜加工後のSIM像を示す。0°加工の場合(Fig.9(a))は数箇所でESD破壊が発生し、パッシバーション膜がクレーター状にえぐられていることがわかる。一方、60°傾斜加工の場合(Fig.9(b))は、ESD破壊は発生しておらず加工領域下面はほぼフラットであるため、60°傾斜加工後に下層配線を問題なく回路修正することが可能である。

試料傾斜により試料表面でのビーム径は傾斜方向に $1 / \cos\theta$ 広がることから、ビーム電流密度は試料傾斜角60°の場合、0°に比較して1/2に低下している。しかし、垂直照射の場合、電流密度を約2桁低下させたデフォーカスビームを用いた実験でもESD破壊が生じることから、試料傾斜に伴うビーム電流密度の低下がESD破壊防止の要因ではないことを確認している。また、XeF<sub>2</sub>およびW(CO)<sub>6</sub>ガスを用いた実験結果から、ガスの種類に関わらずFIB加工部周辺におけるガス分子の存在が試料傾斜加工によるESD破壊防止メカニズムに深く関与していることも確認している。帯電は試料への電荷の出入バランスの崩れにより生じるため、以下ではイオン注入深さ、後方散乱イールド、二次電子放出率、エッチレートの試料傾斜角依存性を評価することにより、試料傾斜によりESD破壊が防止できるメカニズムを考察する。

Fig.8

Dependence of frequency of ESD occurrence on tilting-angle during FIB gas assisted etching with XeF<sub>2</sub>. For each experimental condition, FIB processing was performed five times.

Fig.9

Scanning ion micrographs taken after FIB gas assisted etching with XeF<sub>2</sub> for (a)  $\theta = 0^\circ$  and (b)  $\theta = 60^\circ$ .

## 5-2 試料傾斜加工によるESD破壊防止メカニズム

まず、モンテ・カルロシミュレーションにより30keV Gaイオンを $\text{Si}_3\text{N}_4$ 単層に照射した際のイオン注入深さ、および後方散乱イールドの試料傾斜角依存性を評価した。その結果、60°までの試料傾斜に対してイオン注入率はほぼ一定であり、イオン注入による帯電への影響も一定と考えてよいことがわかった。

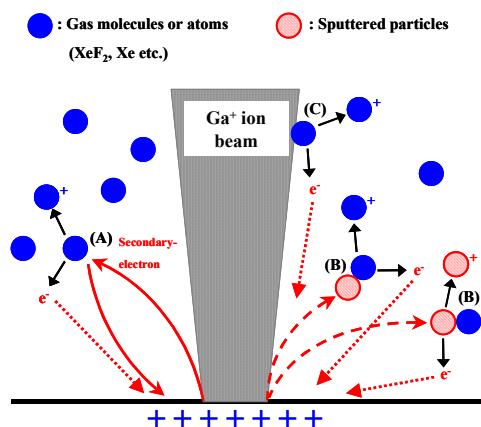

次に、二次電子放出率( $\gamma$ )の試料傾斜角依存性を、接地されたAl製ステージにFIBを照射することで評価した。その結果、 $\gamma$ は試料傾斜角とともに増加し60°では0°の場合のほぼ2倍に達することがわかった。FIBによる $\text{XeF}_2$  GAEの場合、二次電子放出が試料帯電に及ぼす影響は、(1)二次電子放出それ自体、(2)二次電子とガス分子・原子との衝突(Fig.10 (reaction A) 参照)、の2つが考えられる。図中には、ガス分子・原子とスパッタ粒子との衝突(B)、およびガス分子・原子と $\text{Ga}^+$ イオンとの衝突(C)も示している。二次電子放出自体は試料表面をプラス帯電させる方向に働くが、放出二次電子の再配分やパッシベーション膜のESD破壊電圧が約1kVであることなどを考慮すると、(1)の二次電子放出自体はESD破壊には影響を与えていないと考えられる。

Fig.10 Illustration of collisions of gas molecules or atoms with secondary-electrons (A), sputtered particles (B) and  $\text{Ga}^+$  ions (C) during FIB gas assisted etching with  $\text{XeF}_2$ . These collisions induce ionization of the gas molecules, atoms and sputtered particles. Redistribution of secondary-electrons is also shown.

一方、 $\gamma$ は試料傾斜とともに増加することから、(2)の二次電子とガス分子・原子との衝突は試料傾斜角が大きいほど増加する。さらに、試料傾斜角が大きい時には、より多くの二次電子が試料表面近傍で発生するため、放出二次電子の平均エネルギーも試料傾斜角が大きいほど増加する。本実験の $\text{XeF}_2$  GAEの場合、FIB加工部周辺には $\text{XeF}_2$ 、 $\text{Xe}$ が主要なガスとして存在しており、それらの一部は放出二次電子により電子衝撃イオン化していると考えられる。したがって、二次電子との衝突による $\text{XeF}_2$ 、 $\text{Xe}$ のイオン化確率は試料傾斜とともに増加し、その結果FIB加工部周辺で生じた低エネルギー電子がプラス帯電領域に再配分されることで帯電を防止するように働いていると考えられる (Fig.10 (A)参照)。ガスの電子衝撃イオン化により発生する低エネルギー電子の数を概算した結果、入射イオン1個当たり0.35 ( $\theta = 0^\circ$ )、0.69 ( $\theta = 60^\circ$ ) となった。ESD破壊を防止するためにはイオン注入によるプラス電荷のみを中和すればよいが、ガスのイオン化により発生する低エネルギー電子の数は $\theta = 60^\circ$ においても0.69 (<1) であり十分ではない。したがって、試料傾斜加工によるESD破壊防止メカニズムを説明するためには、二次電子とガス分子・原子との衝突に加え、他の要因を考慮に入れる必要がある。

二次電子放出率と同様、エッチレートも試料傾斜とともに増加することが期待される。試料傾斜加工の効率性およびスパッタ粒子の試料帯電への影響を調べるため、エッチレートの試料傾斜角依存性を評価した。その結果、 $\text{XeF}_2$  GAEの場合、試料傾斜を60°にすることで0°と比較しパッシベーション膜のエッチレートを約1.5倍增速でき、効率的なFIB加工が可能であることがわかった。スパッタ粒子が試料帯電に及ぼす影響としては、(1)スパッタ粒子の放出それ自体、(2)スパッタ粒子とガス分子・原子との衝突 (Fig.10 (reaction B) 参照)、の2つが考えられる。しかし、スパッタ粒子のうち90%以上は中性であるため、スパッタ粒子の放出自体による試料帯電への影響は無視できる。一方、エッチレートおよびスパッタ粒子の平均エネルギーは試料傾斜とともに増加することから、スパッタ粒子 (今回の場合、主に $\text{SiF}_4$ 、 $\text{N}_2$ ) とガス分子との衝突に

よるこれらのイオン化確率は試料傾斜とともに増加し、その結果FIB加工部周辺で生じた低エネルギー電子がプラス帶電領域に再配分されることで帶電を防止するようになっていていると考えられる（Fig.10（B）参照）。ガスおよびスパッタ粒子のイオン化により発生する低エネルギー電子の数を概算した結果、入射イオン1個当たり0.48（ $\theta = 0^\circ$ ）および1.37（ $\theta = 60^\circ$ ）となった。したがって、 $60^\circ$ の傾斜加工時にはESD破壊を防止するのに十分な数の低エネルギー電子が発生している可能性が高いと考えられる。

以上の考察から、 $XeF_2$  GAE時の試料傾斜加工によるESD破壊防止メカニズムは次のようにまとめることができる。FIBを試料に対して斜め照射した場合、垂直照射した時と比較して、より多くの二次電子およびスパッタ粒子が、より高エネルギーで放出される。これにより、中性ガスおよびスパッタ粒子のイオン化確率が増加し、より多くの低エネルギー電子がFIB加工部周辺で発生する。この低エネルギー電子が再配分されることで、FIB照射によるプラス帶電を中和していると考えられる。

## 6. デバイス・加工の種類に最適な帯電防止技術の提案

今回開発した3手法の特徴をTable 1に示す。手法(1)は、付加時間ほぼゼロでデバイス特性シフトを防止できる帶電防止効果を有するが、適用可能なFIBプローブ電流の上限は500pAである。一方、手法(2)はnAオーダーの大電流FIB加工にも適用でき、デバイス特性シフトを防止できる帶電防止効果を有するが、10分程度の所要時間を要する。これらに対し、手法(3)は付加時間ほぼゼロでnAオーダーの大電流FIB加工に対してもESD破壊防止は可能だが、デバイス特性シフトを防止できるほどの帶電防止効果は有していないと考えられる。これらの特徴を考慮し、デバイス・加工の種類に最適な3手法の使い分けをTable 2に提示する<sup>10)</sup>。

Table 1 Features of three antistatic techniques for suppressing FIB-induced charging.

| 帯電防止技術             | 付加時間    | 適用可能なFIB電流 | 帯電防止効果      |

|--------------------|---------|------------|-------------|

| (1)500 eV FEB法     | ≈ 0     | < 500 pA   | デバイス特性シフト防止 |

| (2)マイクロプローブ+FIBデボ法 | <10 min | < 20 nA    | デバイス特性シフト防止 |

| (3)試料傾斜加工法         | ≈ 0     | < 20 nA    | ESD破壊防止     |

Table 2 Application criterion of three antistatic methods to realize successful and efficient circuit edits of various devices without FIB-induced charging in same FIB-SEM combined system.

| デバイス | FIB加工                     | 帯電防止技術          |

|------|---------------------------|-----------------|

| アナログ | 大面積加工（ $> 20 \mu m^2$ ）   | マイクロプローブ+FIBデボ法 |

|      | 上記以外                      | 500 eV FEB法     |

| ロジック | 上層大面積加工（ $> 20 \mu m^2$ ） | 試料傾斜加工法         |

|      | 下層大面積加工（ $> 20 \mu m^2$ ） | マイクロプローブ+FIBデボ法 |

|      | 上記以外                      | 500 eV FEB法     |

## 7. 結論

FIBによる回路修正時に生じるESD破壊、デバイス特性シフトを防止する帶電防止技術として、以下の3手法を開発した。

- (1) 500eV収束電子ビームを用いた帶電中和技術

- (2) マイクロプロービングおよびFIBデボ機能を用いた帶電防止技術

- (3) 試料傾斜加工によるESD破壊防止技術

これら3手法の帶電防止効果およびメカニズムを明らかにし、デバイス・加工の種類に最適な3手法の使い分けを提示した。これにより、各種アナログ/ロジックデバイスの回路修正を、同一装置内で帶電によるデバイス特性シフトを防止し、かつ効率的に実施することが可能になった。

## 謝辞

本研究の遂行に際し、多大なるご指導／御協力と有益なる御討論を頂きました大阪大学大学院工学研究科精密科学・応用物理学専攻、エスアイアイ・ナノテクノロジー株式会社、セイコーライ・テクノリサーチ株式会社の関係各位に深く感謝致します。

## 参考文献

- 1) K. N. Hooghan et al. : Integrated circuit device repair using FIB system -tips, tricks, and strategies-, Proc. Int. Symp. Testing and Failure Analysis, (1999), pp.247-254.

- 2) A. N. Campbell et al. : Effects of focused ion beam irradiation on MOS transistors, Proc. Int. Rel. Phys. Symp., (1997), pp.72-81.

- 3) J. Benbrik et al. : Focused ion beam irradiation induced damages on CMOS and bipolar technologies, Proc. Int. Symp. Testing and Failure Analysis, (1998), pp.49-55.

- 4) A. N. Campbell et al. : Focused ion beam induced effects on MOS transistor parameters, Proc. Int. Symp. Testing and Failure Analysis, (1999), pp.273-281.

- 5) H. Komoda et al. : Novel charge neutralization techniques applicable to wide current range of FIB processing in FIB-SEM combined system, Microelectronics Reliability Vol.46, (2006), pp.2085-2095.

- 6) H. Seiler : Secondary electron emission in the scanning electron microscope, J. Appl. Phys., Vol.54, No.11 (1983), pp.R1-R18.

- 7) H. Fujioka, K. Nakamae and K. Ura : Core model for potential distribution on insulator surfaces in the scanning electron microscope, Proc. Int. Cong. Electron Microscopy, (1986), pp.643-644.

- 8) H. Komoda et al. : Antistatic technique for suppressing charging in focused ion beam systems using microprobing and ion-beam-assisted deposition, Jpn. J. Appl. Phys., Vol.44, Part1, No.11 (2005), pp.7907-7909.

- 9) H. Komoda et al. : Sample tilting technique for preventing electrostatic discharge during high-current FIB gas-assisted etching with XeF<sub>2</sub>, Microelectronics Reliability Vol.47, (2007), pp.74-81.

- 10) H. Komoda, Doctoral thesis, Osaka university, (2006).

- 注 1) FIB-SEM 複合装置 SMI2050MS2, SMI3050SE はエスアイアイ・ナノテクノロジー社の商標です。