# パッケージ応力による小型アナログICの回路特性変動評価

## Prediction of Stress-Induced Characteristic Changes for Small-scale Analog IC

上田 尚宏\* 渡辺 博文\*\*

Naohiro UEDA Hirobumi WATANABE

### 要　　旨

アナログ特性の精度向上に伴って樹脂封入（パッケージング）による僅かな特性変動が無視できなくなってきた。今回、1辺1mm未満の小型アナログ集積回路（IC）において、樹脂封入した後の残留応力が引き起こす回路特性の変動を、新たに開発した評価方法を用いて予測する手法を開発した。テストチップは小型ICと同じ外形寸法で、シリコン単結晶中に不純物拡散法で形成した1つの微小なピエゾ抵抗体を備えている。このテストチップの抵抗値変化量を測定することでパッケージ起因の応力変化を検出する。小型ICは外部との接続電極数が少ないので同じ構造のテストチップでは1チップで1箇所の抵抗値しか採取できない。そこで我々はピエゾ抵抗体のチップ内位置を変えた複数のテストチップを作製し、その全ての結果を積算することで1つのチップ面内依存性を再生できることを明らかにした。この新しい手法を用いた小型アナログICのチップ表面応力分布について報告する。さらに、この応力分布を反映したチップ全体の回路特性シミュレーション法を紹介する。

### ABSTRACT

Stress-induced parametric changes during the resin-molded packaging of a small-scale integrated circuit (IC), which is smaller than 1.0 mm<sup>2</sup>, have been evaluated by a new methodology with specially designed test chips. Multiple test chips with different resistor locations have been fabricated, measured by die-to-die correspondence and one contour plot was reproduced from all of the measurement results. This paper shows distributions of parametric change for the small scale ICs. In addition, a new method for evaluating the circuit performance change due to stress-induced parametric changes is presented.

\* 電子デバイスカンパニー 技術開発部

Process Development Department, Electronic Devices Company

\*\* 電子デバイスカンパニー 製品開発部

Product & Technology Development Department, Electronic Devices Company

## 1. 背景と目的

近年の携帯用電子機器の目覚しい普及拡大に伴い、それに用いられる電子機器は小型化が要求され半導体集積回路（Integrated Circuit：以下IC）もその例外ではない。小型化と同時に高精度化への要求も高く、例えば、アナログICの初期精度を高めることや特性バラツキを抑えることがここ数年のデバイス開発の大きな技術課題となっている。

ICの電気特性の高精度化を阻害する1つの要因としてモールドパッケージング工程に伴う特性変動が挙げられる。これは線膨張係数の大きい樹脂がその形成過程で硬化収縮を起こし、その結果、IC表面に圧縮応力が発生することが原因である。この応力によるピエゾ効果で各種デバイスの電気特性は変化し、結果として回路特性もパッケージング工程前後で変化する<sup>1), 2), 3)</sup>。

通常の回路設計はウェハ状態で抽出したSPICEパラメータ<sup>4)</sup>を用いているのでこの特性変動は考慮されていない。

我々は過去に報告例のない1辺1mm未満の小型ICの面内応力評価方法を開発した。また、この技術を用いてモールドパッケージング工程で生じる残留応力起因の回路特性変動を調査したので報告する。

## 2. 技術

### 2-1 テストチップ

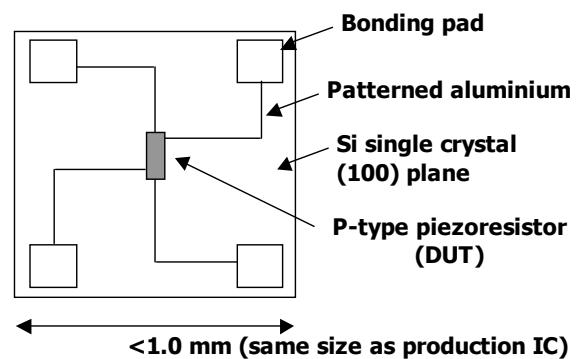

今回の評価で用いたテストチップの外観をFig.1に示す。テストチップは小型ICと同一の形状、同一の接続端子部（Bonding Pad）を備えている。これは実際の小型ICで生じる残留応力起因の特性変動をできるだけ正確に計測するためである。

小型ICは端子数が少なく例えば1辺1mm未満の小型ICでは端子部が4つしかない。よってこれと同じ端子数で作製したテストチップには、応力検出用の素子（ピエゾ抵抗体<sup>5)</sup>）が1つしか搭載できない。つまり、このチップだけでは小型ICのチップ表面の異なる場所の応力データを採取することはできない。

Fig.1 Test Chip.

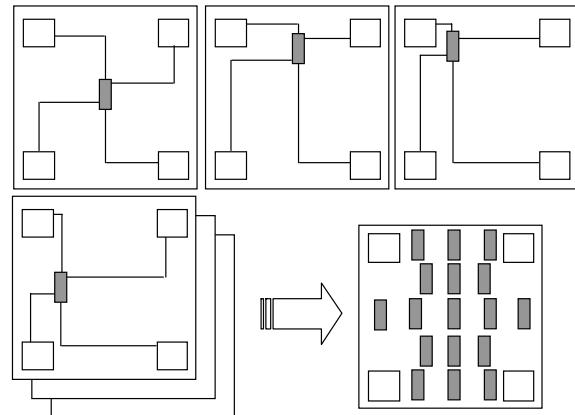

チップ表面の複数の応力データを抽出するために我々は以下3つの工夫をテストチップに盛り込んだ。

第1に、ピエゾ抵抗体の位置をあらかじめ変えた複数のテストチップを同時に形成し、全ての測定結果を1つのチップ平面内に同時に表示する、という手法を採用了。この方法を用いることで端子数が限定された小型ICについても、チップ面内の特性変動傾斜を採取することができるようになった（Fig.2）。

Fig.2 principle of the multi point measurements utilizing the test chips.

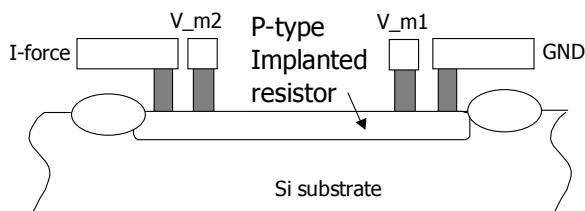

第2として、異なる複数のテストチップの結果から1つのチップの応力面内分布を再現するためには、個々の測定結果に高い測定精度が必要である。このためにテストチップに形成したピエゾ抵抗体の抵抗値測定は、引き回しのメタル配線抵抗の違いやコンタクト抵抗のバラツキなどの外乱要因を排除することができる4端子

法 (4 point Kelvin resistance measurement method<sup>6)</sup>) を用いた (Fig.3) .

第3としては、前述のように評価の対象となる小型ICのチップサイズが1辺1mm未満と極めて小さいのでテストチップに内蔵させるピエゾ抵抗体はチップサイズに対して十分小さい必要がある。そこで今回作製したピエゾ抵抗体は、幅：2um、長さ：30umと極めて小さいものとした。

Fig.3 outline of a piezo sensor cell.

以上の特徴を備えたテストチップを実際の小型ICと同じ生産設備・同じ材料・同じ工程条件でSiウェハ上に作製し、続いてパッケージング処理を行った。抵抗値の測定は温度依存性で生じる測定値バラツキを避けるために、 $23 \pm 0.5^{\circ}\text{C}$ の恒温環境下で行った。

## 2-2 キャリブレーション

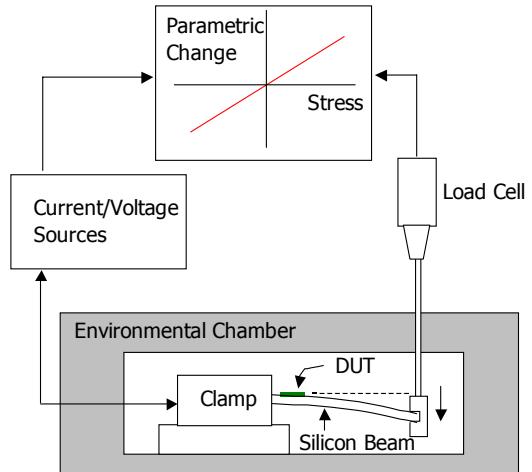

以上の手法で作られたピエゾ抵抗体の抵抗値変動から、回路全体での特性変化を予測するため、回路で用いられているそれぞれの素子の特性変動と、応力に対応して変化するピエゾ抵抗値との相関関係を調査した。

評価システムは短冊形状に切り出したSiチップ ( $10 \times 40\text{mm}$ ) の片側を固定し、自由端側に既知の荷重を印加しながら電気特性を測定する、いわゆるカンチレバー法<sup>7), 8)</sup> を用いた (Fig.4) . 内部応力は印加した荷重とサンプル形状から算出する。

測定は応力の方向と素子に流れる電流の方向が平行な状態で行った。印加した荷重はチップ内応力換算では $0 \sim \pm 150\text{Mpa}$ である。

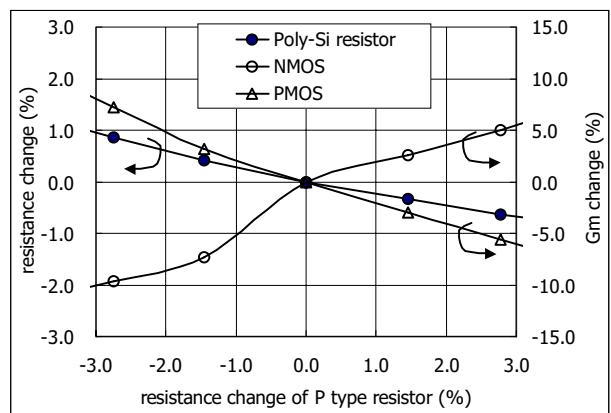

評価結果をFig.5に示す。ピエゾ抵抗体はP型抵抗体で形成した。横軸が抵抗値の応力起因特性変動を、縦軸が同じ応力印加状態での各素子の特性変動を表している。

Fig.4 calibration equipment by cantilever technique.

Fig.5 calibration result.

### 3. 成果

#### 3-1 測定データの精度と再現性

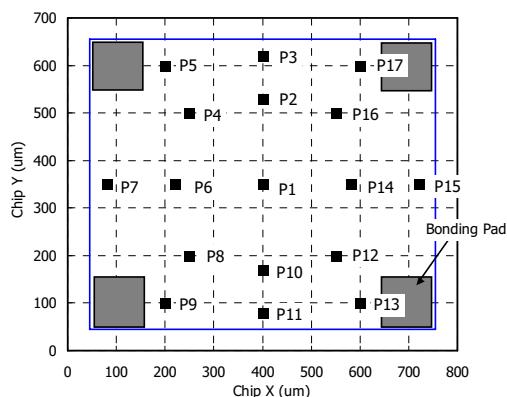

複数のテストチップの測定結果から1つのチップ面内依存性を再現するためには、個々の測定結果に高い精度と再現性が要求される。Fig.6はチップサイズ $0.8 \times 0.7\text{mm}$ のテストチップにおける合計17個のピエゾ抵抗体(P1~17)の配置図である。

Fig.6 configuration of piezo sensor cells for  $0.8 \times 0.7\text{mm}$  test chip.

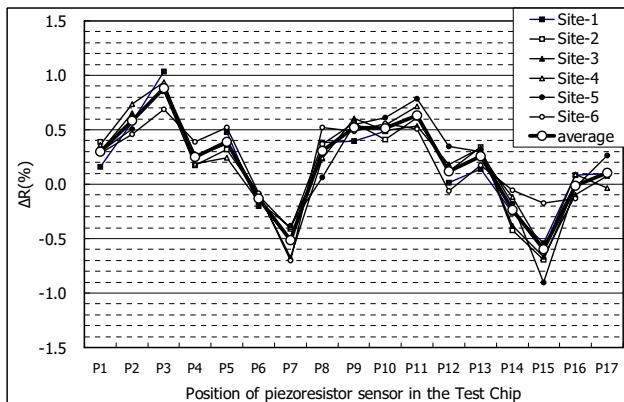

1枚のウエハ内の異なる6つの場所(Site1~Site6)からそれぞれ17個のテストチップを採取し、合計102個のパッケージングに伴う抵抗値変化率 $\Delta R$ を測定した結果をFig.7に示す。

Fig.7 stress-induced resistance change results of 102 packages of the test chip.

ピエゾ抵抗体のチップ内位置(P1~17)に対してSite1~6の測定結果が小さなバラツキ範囲内で同じ挙動を示しており、抵抗値変動のチップ面内依存性が再現性良く高分解能で測定できていることがわかる。

他のチップサイズに対しても同様の結果が得られていることから、我々の評価手法が小型チップの調査に対して十分な精度と再現性をもっていることが確認できた。

#### 3-2 応力起因の特性変動分布

今回、我々が評価したテストチップのチップサイズとセンサー個数、及び、パッケージ種類をTable 1に示す。チップサイズは $0.5 \times 0.5\text{mm}^2$ ,  $0.7 \times 0.8\text{mm}^2$ の2種類、パッケージはA, Bの2種類に対して評価を行った。

Table 1

| Chip size   | $0.5 \times 0.5\text{mm}^2$ | $0.8 \times 0.7\text{mm}^2$ |

|-------------|-----------------------------|-----------------------------|

| N of sensor | 20                          | 17                          |

| Package A   | Figure 8                    | Figure 9                    |

| Package B   | —                           | Figure 10                   |

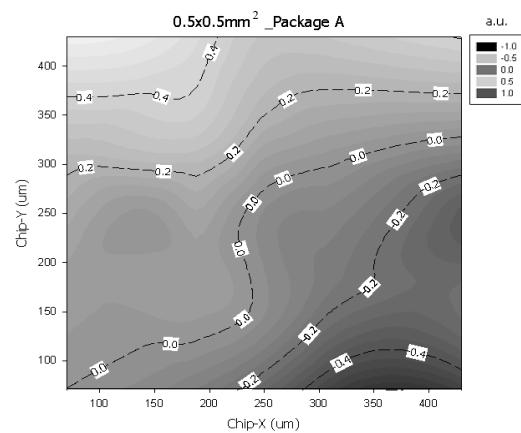

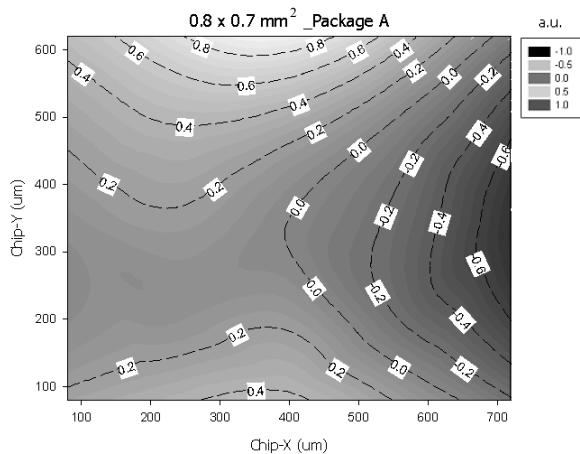

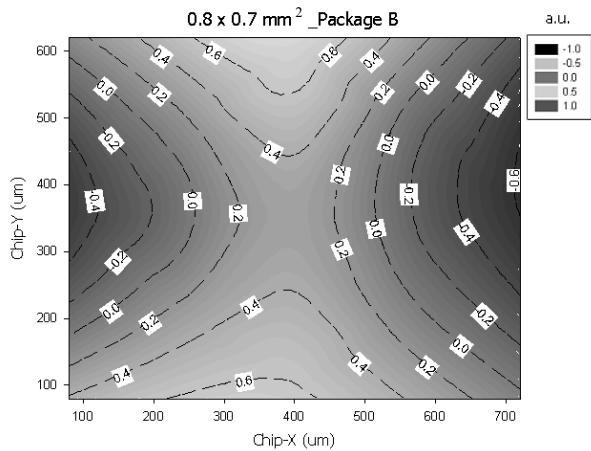

Fig.8~10は実測データを基に計算したピエゾ抵抗体の抵抗値変化率のチップ面内分布であり、図中の数値は抵抗値変化率：(a.u.)を表している。

Fig.8 contour plot of parametric change for  $0.5 \times 0.5\text{mm}$  Si chip resin-molded with package A.

Fig.9 contour plot of parametric change for 0.8×0.7 mm Si chip resin-molded with package A.

Fig.10 contour plot of parametric change for 0.8×0.7 mm Si chip resin-molded with package B.

パッケージ Aに関してチップサイズの異なる2つの分布を比較すると、チップの右領域でマイナス方向の抵抗値シフトが、チップの上領域でプラス方向の抵抗値シフトが共通して観測されている。しかしチップの左下は異なる分布を示している。

パッケージ Aの分布に対してパッケージ Bではチップ中心を原点とした対称的な特性変動傾斜を呈している。

以上のことからパッケージの違いによる特性変動の違いは、パッケージの構造的な違い、特にICチップが接着されているチップタブとそれとつながるリードフレームの形状が原因と考えている。

さらにパッケージ Aで見られた分布の非対称性はキャビティへの樹脂注入が一要因として考えられ、今後の更なる解析が待たれている。

### 3-3 回路特性の変動予測

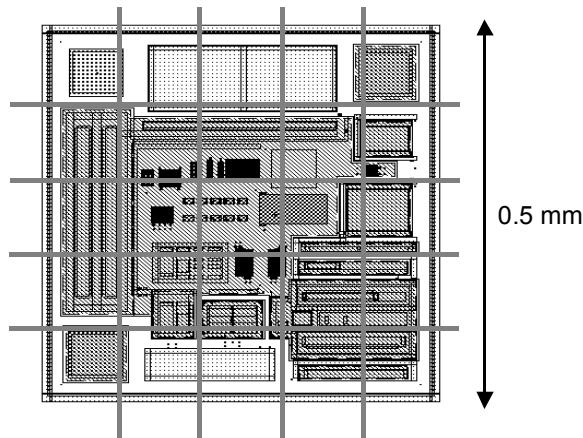

以上の結果を用いてパッケージング工程に伴う特性変動を回路レベルで検証することを試みた<sup>9), 10)</sup>。評価の対象としたテスト回路はチップサイズ：0.5×0.5mmのオペアンプ回路であり、パッケージAで組み立てる想定した。評価手順は以下の通りである。

まず回路全体のレイアウト図を0.1mm単位で正方形分割し、それぞれのブロックに含まれる素子を特定する

(Fig.11)。一方で同じチップサイズの特性変動図も同様に0.1mm単位にブロック分割し、各ブロックにおける特性変動量を読み取っていく(Fig.8)。この時、ブロック内で特性変動量が傾斜を持つ場合は平均値を代表値とした。

特性変動を考慮した素子はNMOS, PMOS, Poly-Si抵抗体の3つであり、トランジスタは伝達関数：Transconductance (Gm)を、抵抗体は抵抗値の特性変動をFig.5のデータを用いて反映させた。

次にそれぞれの変動量を考慮したSPICE回路シミュレーション用のモデルパラメータを作成した。モデルパラメータファイルは変動量の大きさごとに複数作成し、ブロックによる変動量の違いに対応できるようにした。

Fig.11 Experimental circuit

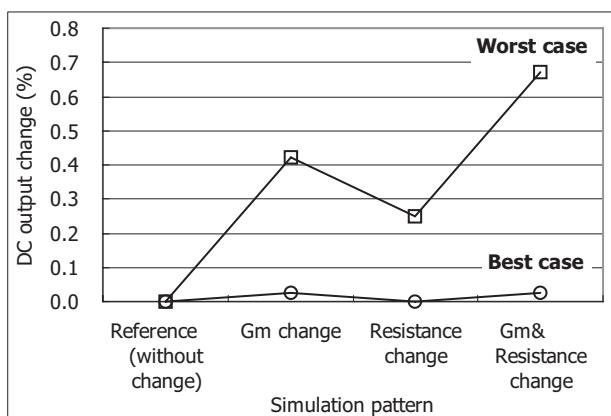

以上の準備をした後、回路シミュレーションを行った。応力の影響で生じる回路のDCアウトプットの変動量をFig.12に示す。

回路シミュレーションは、応力分布を考慮した最適な回路レイアウトの場合をベストケースとし、トランジスタと抵抗体の両方の素子が応力の影響を最大に受ける場合をワーストケースとして、それぞれ実行した。

ワーストケースの場合、DCアウトプットが約0.7%変動する結果が得られた。

Fig.12 Simulation results.

この結果について個々の要因を分離して調査したところ、トランジスタだけが応力の影響を受けて特性変動するとした場合（抵抗値は一定）で約0.4%，一方で、抵抗体のみが変動する場合（トランジスタは一定）は約0.3%出力が変動することが確認できた。

すなわち、この回路においては抵抗体よりもトランジスタのほうが、DCアウトプットの変動に与える影響が大きいことが分かった。

#### 4. 結論

チップサイズが1辺1mm未満の小型ICに対してモールドパッケージング工程に伴う応力起因特性変動を評価した。評価に当たってはピエゾ抵抗体のチップ面内位置を変えた複数のテストチップを作製し、その全ての結果から1つのチップ面内分布を再現する、という独自の手法を開発した。

本手法を用いることで、チップサイズが異なると応力の面内分布が異なること、パッケージ種類に関してもチップ面内分布を左右することが明らかになった。

これらの結果を用いてチップ全体の回路特性変動をシミュレーションしたところ、素子によって影響度合いが異なることが確認できた。

以上のことから、我々が開発した手法は端子数が限定された小型ICのパッケージング起因の特性変動評価に対して極めて有効であることが示された。

#### 5. 今後の展開

本技術を実際のIC回路設計に適用することで従来品の性能を上回る超高精度なICが実現できる。

さらにこの技術は小型ICに対して応力分布の可視化を可能としたことで様々な産業分野への応用が可能であり、例えば、低応力パッケージングに関する実装技術開発、さらにはそれに用いる新規樹脂開発などへの応用が期待できる。

## 参考文献

- 1) H. Ali : "Stress-Induces Parametric Shift in Plastic Packaged Devices" IEEE Transactions on Components, Packaging, and Manufacturing Technology, Part B, vol.20, No.4, Nov., (1997).

- 2) Y. Kanda, "A Graphical Representation of Piezoresistance Coefficients in Silicon," IEEE Transactions on Electron Devices, vol.ED-29, No.1 (1982), pp.64-70.

- 3) A. Hamada et al. : "A new aspect of mechanical stress effects in scaled MOS devices," IEEE Transactions on Electron Devices, vol.38, No.4 (1991), pp.895-900.

- 4) <http://bwrc.eecs.berkeley.edu/Classes/IcBook/SPICE>

- 5) Jeffrey C. Suhling and Richard C. Jaeger : "Silicon Piezoresistive Stress Sensors and Their Application in Electronic Packaging," IEEE Sensors Journal, vol.1, (2001), pp.14-30.

- 6) [http://www.allaboutcircuits.com/vol\\_1/chpt\\_8/9.html](http://www.allaboutcircuits.com/vol_1/chpt_8/9.html)

- 7) F. Fruett, G. C. M. Meijer and A. Bakker : "Low-drift Bandgap Voltage References," European Solid-State Circuit Conference, (2002).

- 8) F. Fruett and G. C. M. Meijer : "The Piezojunction effect in silicon integrated circuits and sensors, " ISBN 1-4020-7053-5, Kluwer Academic Publishers.

- 9) S. Komatsu et al. : "Stress-insensitive diffused resistor network for a high accuracy monolithic D/A converter," in IEDM Tech. Dig., Int. Electron Devices Meet., (1980), pp.144-148.

- 10) H. Miura : "Device Characteristic Changes Caused by Packaging Stress," Mechanics and Materials for Electronic Packaging, AMD-Vol.195, (1994), pp.101-109.