# LDMOSトランジスタを用いた電圧レギュレータの開発

Development of Voltage Regulator using LDMOS Transistor

根来 宝昭\*

Takaaki NEGORO

## 要　　旨

24V以上の高電圧動作の電圧レギュレータでは近年、低消費電流製品としてCMOS製品が注目を浴びている。しかし、従来の高耐圧MOSトランジスタはON抵抗を小さくすることが難しく、バイポーラ製品に対抗できる製品を実現することが困難であった。今回、低ON抵抗の特徴をもつ高耐圧LDMOS（横方向拡散型MOS）トランジスタを出力トランジスタとして採用して大電流LDO（低ドロップアウト）電圧レギュレータを実現したので報告する。

## ABSTRACT

CMOS voltage regulators at high voltage operation of 24V or more in power supply IC are watched with interest recently because of the low current consumption. The difficulty to achieve low on resistance of high voltage MOS transistor inhibits the production of LDO (Low dropout) CMOS voltage regulators with large current comparable to Bipolar driver, does not produced. We developed a new large current voltage regulator using high voltage LDMOS (Lateral diffused MOS) transistor. Device feature and performance of voltage regulator are described in this paper.

\* 電子デバイスカンパニー 製品開発部

Analog Design Development Section, Electronic Devices Company

## 1. 背景と目的

安定化電源回路のひとつに電圧レギュレータがある。この製品はバイポーラ型電圧レギュレータ<sup>1), 2)</sup>とMOS型電圧レギュレータ<sup>1)</sup>に大別される。MOS型電圧レギュレータは消費電流を抑えることが可能であることが特徴である。加えて、携帯機器分野では閾値電圧の制御により低電圧動作化、微細化技術によりチップ面積の小型化を図ることが可能なMOS型電圧レギュレータが注目されている。

近年、MOS型レギュレータで高耐圧電圧分野の製品も開発されており、特に車載製品に関してはバックアップ用電源などで消費電流の少ない製品が実現されている。しかし、高耐圧製品では低ドロップアウト、高速応答のMOS型製品は実現できておらず、バイポーラ型製品が主流である。しかし、電流入力駆動のバイポーラトランジスタを用いた製品では低消費電流化は困難である。そこで、新たに開発した高耐圧、低ON抵抗のPchLDMOS（横方向拡散MOS）トランジスタ<sup>4), 5)</sup>を搭載した高耐圧電圧レギュレータを開発したので紹介する。

## 2. 技術

### 2-1 MOS型電圧レギュレータ

#### 2-1-1 低ドロップアウト、高速応答のための出力ドライバトランジスタの選定

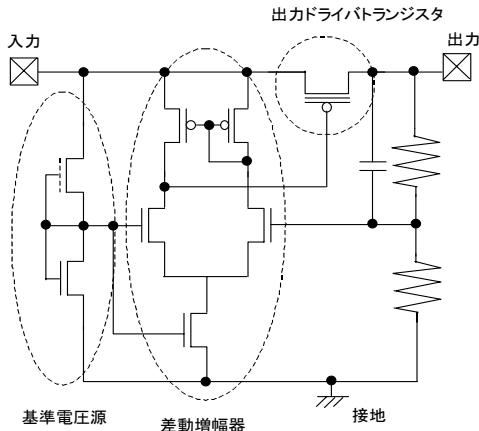

MOS型電圧レギュレータの回路構成をFig.1に示す。基準電圧源、差動増幅器、出力ドライバトランジスタ、抵抗で構成され、出力電圧を監視して負帰還をかけることで出力電圧を安定化している。

低ドロップアウト、高速応答の製品を達成するには各增幅器の利得が高いことが必要で、出力ドライバトランジスタにも低ON抵抗の利得の高いトランジスタが求められる。次にトランジスタの候補としてのMOSトランジスタとバイポーラトランジスタの特性について考察する。

Fig.1 Voltage Regulator circuit.

それぞれのトランジスタの相互コンダクタンス  $gm$  は式(1), (3)のように表される。

$$\text{MOS} : \quad gm = \sqrt{2Id \times \beta} \quad \cdots(1)$$

$$\beta = \frac{W}{L} \times C_{ox} \times \mu \quad \cdots(2)$$

$$\text{バイポーラ} : \quad gm = \frac{Ic}{Vt} \quad \cdots(3)$$

$$Vt = \frac{KT}{q} \quad \cdots(4)$$

ここで、  $Id$  : ドレイン電流  $W$  : チャンネル幅

$L$  : チャンネル長  $C_{ox}$  : ゲート容量

$\mu$  : 移動度

$Ic$  : コレクタ電流

$K$  : ボルツマン定数  $T$  : 絶対温度

$q$  : 電子の電荷量

である。

なお、出力ドライバトランジスタとして使用する場合には  $Id$  と  $Ic$  は回路の出力電流に相当する。バイポーラトランジスタの  $gm$  は物理定数で決定され、MOSトランジスタの  $gm$  はトランジスタの設計値 ( $L$  : チャンネル長,  $W$  : チャンネル幅,  $C_{ox}$  : ゲート容量) によって決定されることがわかる<sup>3)</sup>。一般的な高耐圧MOSトランジスタではチャンネル長を長く、ゲート酸化膜厚を厚くして耐圧を高めるために  $gm$  を大きくすることや低ON抵抗化が困難である。たとえば、バイポーラトランジスタに匹敵する性能を

MOSトランジスタで実現するためにはチャンネル長を $1.0\mu m$ にする必要があるが、 $1.0\mu m$ では高耐圧を実現することは不可能である。そこで、出力トランジスタとして実効チャンネル長が小さくて利得が大きく、かつソース・ドレイン耐圧も大きく設計できるLDMOS（横方向拡散MOS）トランジスタを選定した。ここで、定格電圧35V時のON抵抗を従来の高耐圧MOSトランジスタに対して1/5にすることを目指して開発した。

## 2-2 高耐圧トランジスタ

MOS型高耐圧トランジスタに従来より多く使われてきたLOCOSオフセットMOSトランジスタと本論文で検討した新規のLDMOSトランジスタの2種類がある。本節ではその製造フローと各デバイスについて述べる。

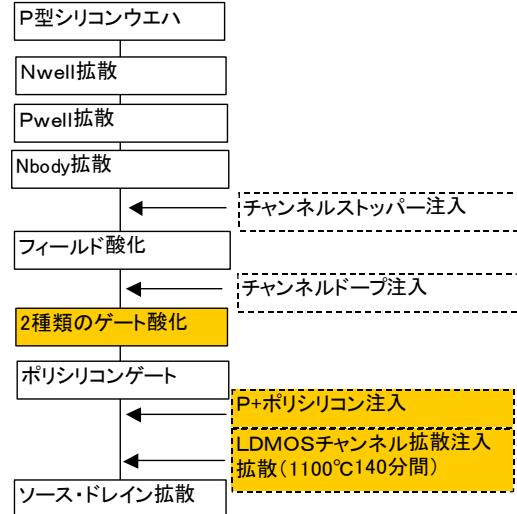

### 2-2-1 LDMOS混載の製造フロー

LOCOSオフセットMOSトランジスタとLDMOSトランジスタを混載できるように2つのトランジスタを同時に作成する製造フローをFig.2に示す。特に重要な点はPchLDMOSトランジスタをつくるためにポリシリコンゲート電極をつけた後にチャンネル拡散（ $1100^{\circ}\text{C}140\text{分}$ ）を行う工程を追加したことである。この熱処理でチャンネルドープ拡散の再分布が生じる。また、埋め込みチャンネル型MOSトランジスタでは閾値電圧を下げる事が難しいため、Nchトランジスタはリンデポ<sup>+</sup>拡散によるN型ポリシリコンゲート電極、Pchトランジスタはボロン注入拡散のP型ポリシリコンゲート電極としてNch、Pchトランジスタ共に表面チャンネル型トランジスタとした。

LDMOSを混載するために追加した工程を   で示す。

Fig.2 Process flow.

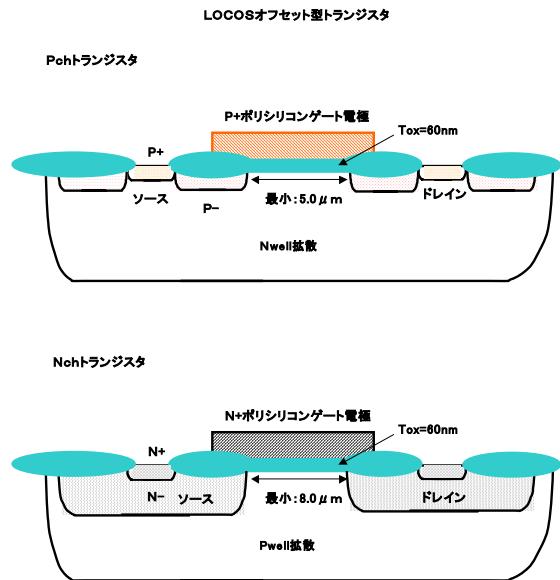

### 2-2-2 LOCOSオフセットMOSトランジスタ

作成したPch、NchLOCOSオフセットMOSトランジスタをFig.3に示す。

Fig.3 Cross-section of the LOCOS OFFSET MOS transistors.

ドレイン端のゲート電極電界を緩和するためにLOCOS酸化膜でゲート電極とドレイン電極の距離を遠ざけるオフセット構造とした。また、PchMOSトラン

ジスタについては、高温熱処理中にポリシリコンゲート電極からチャンネル部にボロン原子が拡散することを防止するために、ポリシリコンゲート電極へのボロン注入の工程を高温熱処理の後のソース・ドレイン拡散工程と同時に実行した。NchMOSトランジスタは高電圧動作時にソース拡散 - ウエル拡散 - ドレイン拡散による寄生バイポーラ動作で破壊することを防止するためにソース・ドレイン拡散はPchMOSトランジスタに比べて深く、また抵抗も低くなるように作成した。

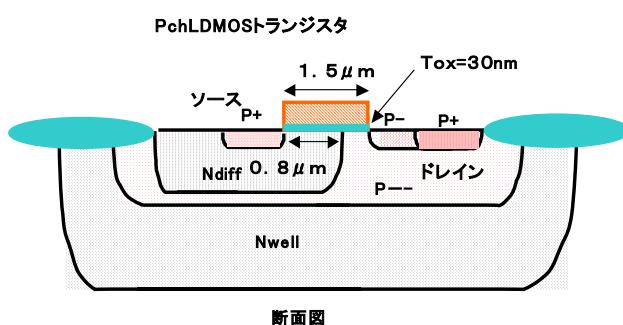

### 2-2-3 LDMOSトランジスタ (Pch)

今回のMOS型電圧レギュレータにおいてLDMOSトランジスタはPchトランジスタのみを搭載することとした。PchLDMOSトランジスタ構造をFig.4に示す。素子間の分離はPchLOCOSオフセットMOSトランジスタを分離するためのNwell拡散を使用した。このNwell拡散層内にPchLDMOSトランジスタを作りこむ拡散濃度条件を最適化して $0.8\mu m$ のチャンネル長としたトランジスタを実現できた。なお、ドレイン抵抗はドレイン電極をとるためのP+拡散とゲート電極との間の表面領域のP-拡散の濃度をコントロールして適当なドレイン抵抗になるようにした。また、低ON抵抗化の観点よりドレイン電流経路を阻害しないようにゲート酸化膜厚はLOCOS酸化膜を用いないで熱酸化膜だけで形成した。

Fig.4 Cross-section of the Pch LDMOS transistor.

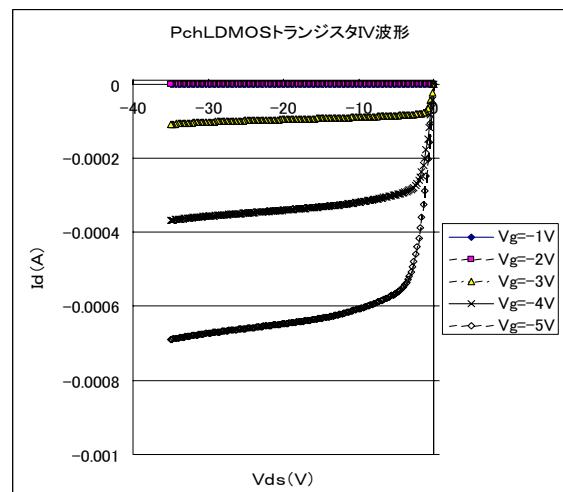

今回試作した35V定格のLDMOSトランジスタで得られた電流電圧波形をFig.5に示す。チャンネル長が $0.8\mu m$ と微細にもかかわらず、 $V_{ds}$ に対する $I_d$ （ドレイン電

流）の変化の少なく、出力抵抗が高い電流変換利得の高いトランジスタを実現できた。

Fig.5 I-V characteristics of the Pch LDMOS transistor.

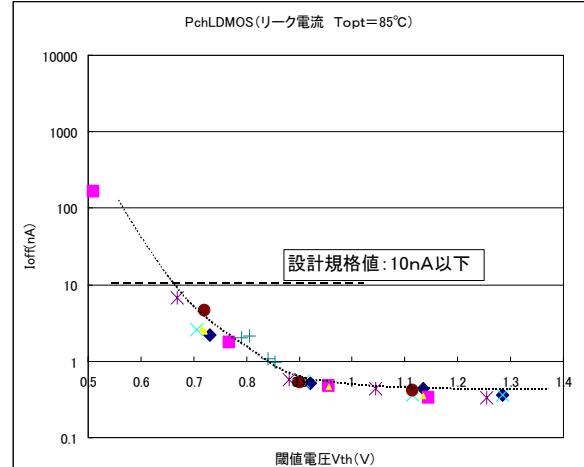

Fig.6にリーク電流の閾値電圧依存性を示す。実用的な-0.8Vまで充分にリーク電流が制御されている。

Fig.6 Leakage current of the Pch LDMOS transistor.

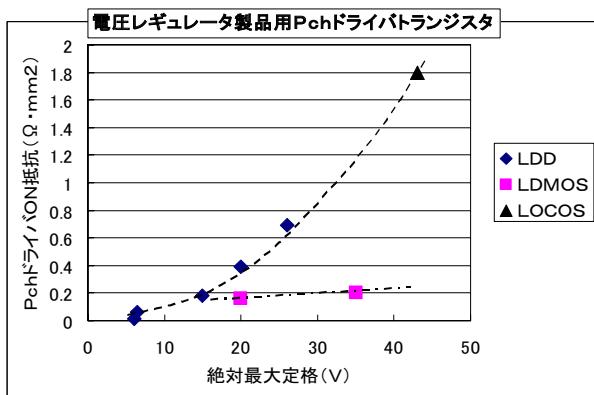

### 2-2-4 LOCOSオフセットMOSトランジスタとPchLDMOSトランジスタのON抵抗

トランジスタの設計値に起因してON抵抗は変化するが、絶対最大定格電圧を満たして最適化した最小レベルのLDD (lightly doped drain) MOSトランジスタと

LOCOSオフセットMOSトランジスタとLDMOSトランジスタのON抵抗の比較をFig.7に示す。定格電圧35Vで、LOCOSオフセットMOSトランジスタのON抵抗に比べ、今回試作したLDMOSトランジスタのON抵抗は約1/6を実現することができた。

LDMOSトランジスタ構造はドレイン拡散濃度を下げて、チャンネル拡散とのPN接合耐圧を大きくすることで、チャンネル長を変化させずに高耐圧化が図れる特徴がある。

Fig.7 On resistance for high voltage MOS transistors.

### 2-3 MOS型電圧レギュレータ

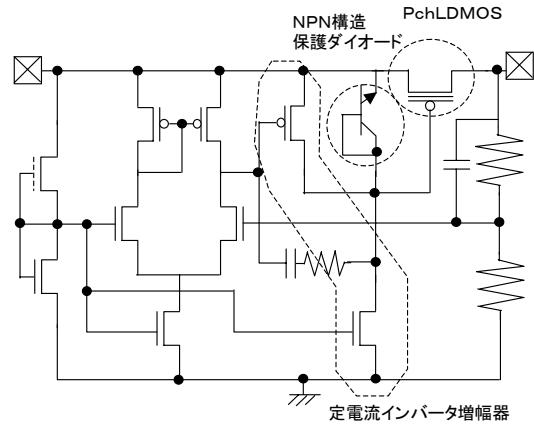

PchLDMOSトランジスタを使った電圧レギュレータ回路をFig.8に示す。

アナログ回路設計ではオフセット電圧の低減が重要である。一般に差動増幅器では2つ以上のトランジスタを全く同じ特性となる様にサイズをそろえて用いる方法がとられるが、それらのトランジスタの特性（特に電流電圧特性）のオフセットが生じないようにMOSトランジスタの場合、チャンネル長を大きくする。

Fig.8 Voltage Regulator circuit using LDMOS transistor.

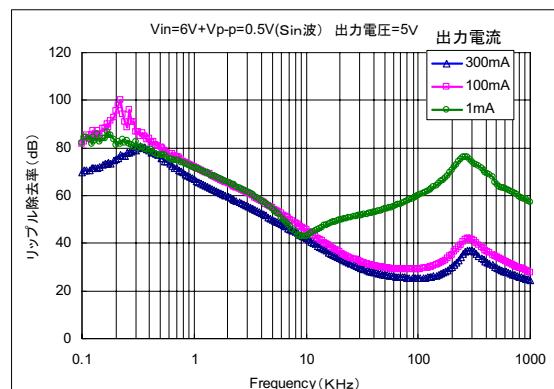

そのため、MOSトランジスタでは相互コンダクタンス  $gm$  が小さくなり差動増幅器の利得が下がるため、バイポーラ回路の利得に及ばなくなる。そこで、Fig.1で説明したMOS型電圧レギュレータ回路は差動増幅回路と出力ドライバで構成する2段増幅回路であるが、今回検討した回路では利得を大きくするために定電流インバータ増幅器を追加して3段増幅回路とした。試作したLDMOSトランジスタ搭載MOS型電圧レギュレータのリップル除去率（入力電圧に含まれる交流成分が、出力電圧で減衰する比率）の測定結果をFig.9に示す。リップル除去率は利得の特性を表す指標であり、定電流インバータ増幅回路を追加することで1kHzでも70dBと高利得をもつ特性が得られた。

Fig.9 Input ripple rejection.

また、相互コンダクタンス  $gm$  の大きいPchLDMOSトランジスタのゲート酸化膜厚はLOCOSオフセット型トランジスタと比べて薄いために、出力電流を最大にする等の過渡的な動作が発生した時に、入力電圧と定電流インバータ増幅器の出力電圧差が最大となり、その電圧がPchLDMOSトランジスタのゲート－ソース電極間にかかるためゲート酸化膜破壊を引き起こす。そこで、ゲート－ソース電極間に約12Vの逆方向耐圧をもつ保護ダイオードを追加してゲート酸化膜破壊を防止した。

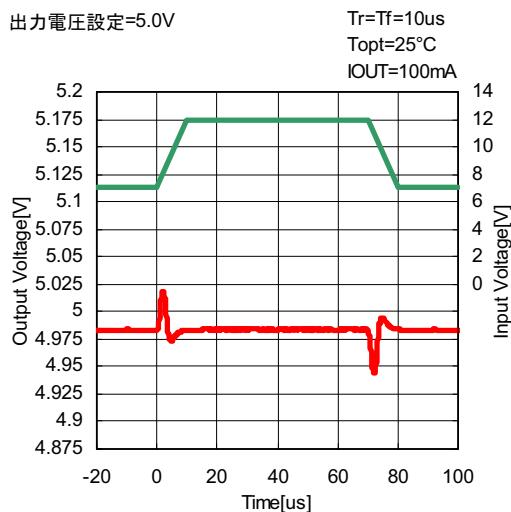

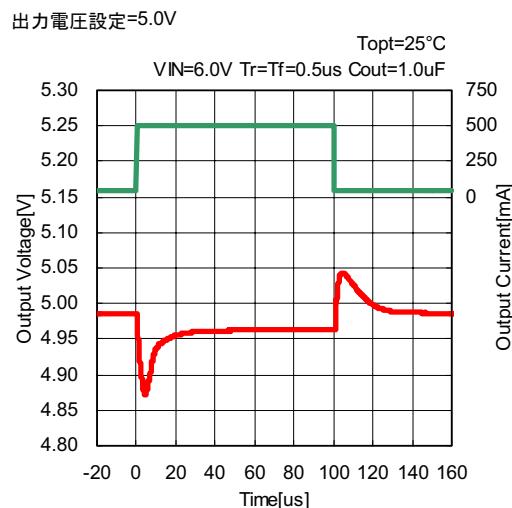

入力電圧過渡応答特性（急激な入力電圧の変化に対する出力電圧変化）と出力電流過渡応答特性（急激な出力電流の変化に対する出力電圧の変化）をFig.10, Fig.11に示す。

上記の保護ダイオードの追加でPchLDMOSトランジスタのゲート電圧に制限がかかり電圧レギュレータの過渡応答特性の劣化が懸念されたが、PchLDMOSトランジスタのゲート容量を充分に充放電できるように定電流インバータ増幅器の定電流値を最適化することで、出力電圧変動が±1.5%以内になり、充分な過渡応答特性が得られた。

Fig.10 Line transient response.

Fig.11 Load transient response.

### 3. 成果

新たに開発した高耐圧、低ON抵抗のPchLDMOS（横方向拡散MOS）トランジスタを搭載した高耐圧電圧レギュレータを開発した。

一般的なバイポーラ製品とMOS製品を比較して報告する。今回開発したLDMOS混載のMOS型電圧レギュレータと市販されているバイポーラ型電圧レギュレータとの比較をTable 1に示す。

Table 1 Electrical characteristics of Voltage regulators.

| 製品名   | 絶対最大(V) | 出力電流(A) | 消費電流(無負荷時) | R.R(1kHz)(dB) | ON抵抗(Ω) |

|-------|---------|---------|------------|---------------|---------|

| A     | 35      | 1       | 8mA        | 55            | 0.5     |

| B     | 20      | 1       | 10mA       | 60            | 0.7     |

| C     | 16      | 1       | 0.8mA      | 63            | 0.3     |

| R1500 | 36      | 0.5     | 70uA       | 60            | 0.7     |

A B Cは市販バイポーラ製品

R1500はLDMOS内蔵CMOS製品(本論文製品)

バイポーラ製品と比較して利得の高さを示すR. R. (リップル除去率) やON抵抗の特性を同等レベルの性能を維持しながら消費電流を1桁以上低減することができた。

## 4. 今後の展開

MOSトランジスタはバイポーラトランジスタと比較して二次降伏がなく高耐圧化を図りやすいので60V帯への高耐圧化が可能である。また、LDMOSトランジスタを用いたCMOS技術を展開して10 $\mu$ A未満のさらなる低消費電流化も同時に検討する。

### 参考文献

- 1) 宮崎誠一：トランジスタ技術増刊 アナログIC活用ハンドブック CQ出版社

- 2) 鈴木正太郎：オンボード電源の設計と活用 CQ出版社

- 3) 佐野芳昭：アナログ集積回路設計の基礎と実際 (株) リアライズ社

- 4) Taylor R. Efland, Chin-Yu Tsai, Sameer Pendharkar : "Lateral Thinking About Power Devices (LDMOS)" IEDM vol.98 (1998) pp679

- 5) M. S. Shekar, Richard K. Williams, Mike Cornell, Min-Yih Luo, Mohamed Darwish : "Hot Electoron Degradation and Unclamped Inductive Swithing in Submicron 60-VLateral DMOS" IRPS vol.98 (1998) pp383